課題および設計 ・ 試作条件

課 題

「高周波高利得増幅器の設計・試作」

増幅器の段数は1または2とし、それぞれ別のカテゴリーで評価、表彰します。

増幅器の段数は1または2とし、それぞれ別のカテゴリーで評価、表彰します。

設計条件

下記の条件を満たすように設計すること。 デザインレビューで満たすべき条件になります。

- 100MHz〜10 GHzにて安定係数 K > 1 となること。

- 100MHz〜10 GHzにて入出力に反射利得を有しないこと、すなわち|S11|< 1 、|S22|<1 であること。

- 下記トランジスタを1または2個使用すること。1応募に対し10個のトランジスタを主催者から支給します。

トランジスタの型番 : Avago社製ATF-54143-BLKG

トランジスタのデータシート等の入手先 :

http://www.avagotech.com/pages/en/rf_microwave/transistors/fet/atf-54143/ - 1GHzをその中に含み、20%の動作比帯域(以下、20%比帯域)を有すること。

評価指標

20%比帯域での最小利得を基底利得と定義し、

ただし、2. 3.では、基底利得が8dB以上(1段増幅器)または16dB(2段増幅器)であることを条件とします。

また、1. 2. 3.では、20%比帯域内でS11、S22が0dBより小さいことを条件とします。

- 基底利得 [大きいほど良い]

- 20%比帯域での利得偏差 [小さいほど良い]

- 消費電力(mW) [小さいほど良い]

ただし、2. 3.では、基底利得が8dB以上(1段増幅器)または16dB(2段増幅器)であることを条件とします。

また、1. 2. 3.では、20%比帯域内でS11、S22が0dBより小さいことを条件とします。

20%比帯域の定義

参加者は、下限周波数A、上限周波数Bを申告します。

このとき、AとBは、下記を満たす必要があります。

20%比帯域として取り扱います。

2. の値が 0.2 から大きく離れた場合、評価上は不利になりますのでご注意ください。

このとき、AとBは、下記を満たす必要があります。

- A ≤ 1GHz かつ B ≥ 1GHz ・・・1GHzを含む

- (B-A) / ((A+B) / 2) ≥ 0.2 ・・・比帯域が20%(以上)

20%比帯域として取り扱います。

2. の値が 0.2 から大きく離れた場合、評価上は不利になりますのでご注意ください。

その他

- トランジスタ以外の使用部材や回路構成は自由。

ただし増幅器はSMAコネクタ(Female)を備え、高周波電力の入出力が行えること。

評価に際しては、ベクトルネットワークアナライザを用いて測定を行います。 - バイアス回路を含むこと。

バイアス回路を含まない場合、バイアスティーを用いて給電しても構わないが、その場合、回路にはバイアスティーを

含むものとする。 - 用意する電源装置の制約から、増幅器に加える電源電圧は0〜5V、最大電流値は60mA(1段あたり)とします。

- 参加者には、設計テンプレート・設計チュートリアルを配布しますので、増幅器設計の初心者でも気軽にご参加ください。

※ Webからのダウンロードを予定。 詳細は、別途応募者宛てに連絡いたします。 - 回路設計ツールが手元にない方には、コンテスト参加用のマイクロ波回路設計CADソフトのデモライセンスを

斡旋いたします - 設計テンプレートに従って試作した場合、回路設計期間1週間、試作・評価期間1週間の合計2週間程度の期間を要

すると見込んでいます。ただし上位入賞を目指してより高度な回路設計に挑戦する場合は、上記以上の期間を要する

可能性がありますので早めのエントリー・着手が有利となります。 - 万が一、試作品評価時に発振が生じてしまった場合、著しく性能が劣化するか、測定値が得られなくなることが考えら

れます。任意の負荷に対して発振しないように設計し、その安定性を事前に確認することを推奨します。

|

|

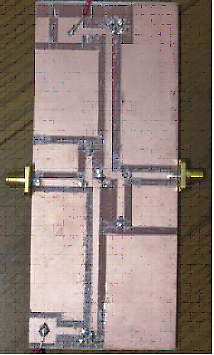

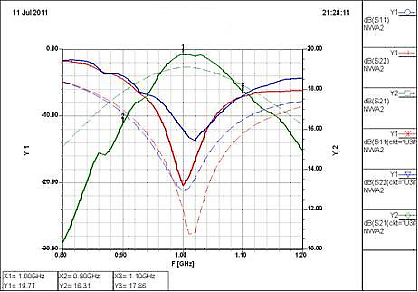

| 1段増幅器の作製例 | 小信号特性 (実線:測定値、破線:設計値) |