# マイクロ波増幅器設計の基礎

- 教科書に書いてある基礎と案外書いてない基礎-

# Introduction to Microwave Amplifier Design

-From Textbook Basics to Practicing Designer's Basics-

#### 石原 昇

#### Noboru Ishihara

東京工業大学 科学技術創成研究院 未来産業技術研究所 FIRST, Institute of Innovative Research, Tokyo Institute of Technology

#### 概要

本稿ではトランジスタ1段のマイクロ波増幅器を例に、教科書では意外と説明されていない理由も含めた高周波増幅回路設計の基本的考え方、勘所を述べる。まず、キーコンポーネントである増幅素子の代表として MOS 型電界効果トランシスタに着目し、その動作特性(直流特性、増幅素子の三定数、等価回路による高周波特性、Sパラメータによる電力利得の高周波特性)について理解を深め、回路設計の要である整合設計とはなにか、インピーダンス/アドミタンスチャートによるインピーダンス整合の取り方、整合設計におけるトランジスタの双方向特性の影響について考える。さらに、システム応用として無線通信で利用されている増幅器の高電力効率化、低雑音化のポイントについても触れる。

# Abstract

The basic design techniques of a microwave amplifier with one transistor are explained. At first, a MOS field effect transistor is focused as a representative of amplifying element and its operating characteristics are deepen in our understanding. And next, it is discussed about importance of impedance matching that is key in the amplifier design, how to perform the matching using an impedance / admittance chart, and the influence of bidirectional transistor characteristic in the matching design. In addition, it is touched on the design points of higher power efficiency and lower noise of amplifiers.

#### 1. はじめに

1906年3極真空管[1]が、1947年にはトランジスタが発明[2]されて以来、エレクトロニクスは、増幅素子であるトランジスタを集積化した回路として飛躍的な進歩を遂げた。現在、我々が使用しているパーソナルコンピュータやスマートフォン、様々なデジタル家電(TV など)に搭載されている中央演算処理集積回路(CPU)には、数千万個以上のトランジスタが搭載されており、それらの無線や有線の通信インターフェースには、マイクロ波帯(数百 MHz 以上)で動作する高周波増幅器が搭載されている。我々の現在のインテリジェントな生活は、天文学的な数の増幅素子により支えられており、その要素であるトランジスタ増幅回路の理解は、エレクトロニクス設計の要である。

本稿では、トランジスタ1段のマイクロ波増幅器を例に、教科書では意外と説明されていない理由も含めた高周波増幅回路設計の基本的考え方、勘所を述べる。マイクロ波帯増幅器では、高周波特性に優れるバイポーラトランジスタ(BIP)や化合物半導体による電界効果トランジスタ(FET)が、増幅素子としてこれまで多く用いられてきたが、製造技術の微細化により、MOSFETでもマイクロ波帯での増幅動作が可能となった[3,4]。そこで本稿では、増幅素子としてMOSFETを例にマイクロ波帯増幅器設計の理解を深めることにする。

# 2. マイクロ波増幅器の基本構成と設計フロー

マイクロ波は波長の短い信号の総称で、一般的に 数百 MHz 以上で動作する高周波信号増幅器をマイクロ波増幅器と呼んでいる。

#### 2.1 マイクロ波増幅器の基本構成

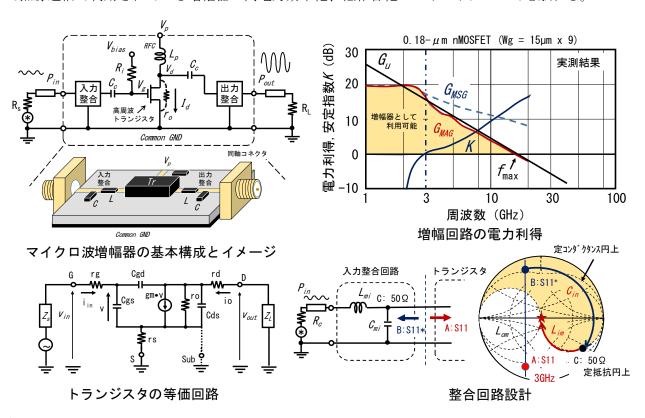

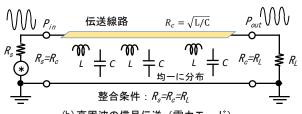

図1にトランジスタ1段のマイクロ波増幅器の基本構成とその物理的イメージを示す。ソース接地増幅回路で、入力信号により出力電流を制御し、出力の負荷により増幅された信号を得る構成である。低周波の増幅器とは、①増幅素子が高周波で動作可能であること、②入出力部にインピーダンス整合回路が付加され、信号の入出力は伝送線路を介して行っていること、③トランジスタ側から見た整合回路のインピーダンスをパラメータとして所望の増幅特性が得られるよう設計されていることが主に異なっている。

マイクロ波増幅器は、数百 MHz から数百 GHz レベルまで、様々な特性の増幅器が実現されており、動作周波数帯や出力電力、雑音などの特性により分類することができる。また、増幅器のイメージを考

図1 マイクロ波増幅器の基本構成とイメージ

表 1 マイクロ波増幅器の使用素子による分類

|   |          | 増幅素子                                                 | 整合回路用素子                           | 最大周波数領域<br>(目安) |

|---|----------|------------------------------------------------------|-----------------------------------|-----------------|

|   | ハイブリッド集積 | デ、ィスクリートトランシ、スタ<br>(パッケーシ、品)<br>設計用モデル<br>Sパラメータデ゜ータ | チップ 部品<br>(R, L, C on chip)       | ~ 3 GHz         |

|   |          |                                                      | 分布定数素子<br>(R,L,C pattern on PCB)  | ~ 数10 GHz       |

| Ī | ŧノリシック集積 | 集積回路用トランジスタ<br>(スケーラブル)<br>設計用モデル<br>等価回路            | 集中定数素子<br>(R, L, C on chip)       | - 10 GHz ~      |

|   |          |                                                      | 分布定数素子<br>(R,L,C pattern on chip) |                 |

えると使用する部品や回路の製造法により表1のように分類することができる。

大別して、増幅素子としてパッケージに封入されたディスクリートトランジスタを用いプリント基板上に構成するハイブリッド構成と集積回路用トランジスタを用いるモノリシック構成に分けられる。整合回路は、集中定数素子と分定数素子を用いる場合に分けられる。チップ部品を用いる場合は、チップ

部ピり~3 GHz をで器ののが帯ではありではよ越動もではない、100 GHz とり、100 GHz をすきながある。 横集は数幅で [5]。

# 2.2 設計フロー

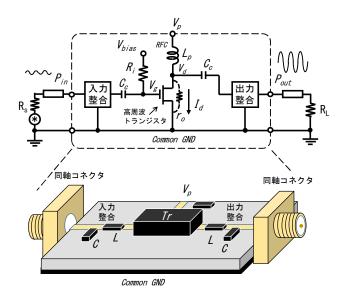

図 2 にマイク ロ波増幅器の設 計フローを示す。

図2 マイクロ波増幅器の設計フロー

目標仕様を設定後、トランジスタの選定を行う。データシートを参考にトランジスタの高周波特性を判断し、設計に必要となるトランジスタパラメータ(等価回路やSパラメータ)を入手する。

マイクロ波増幅回路の設計のポイントは入出力整合設計である。トランジスタの特性、特に入出力インピーダンス特性をベースに整合回路定数を最適化する。

実装設計は回路を具現化するため、ハイブリッド 構成ではプリント基板の設計を行い、モノリシック 構成では、集積回路チップのレイアウト設計、チッ プのパッケージングや基板への実装設計も行う。

設計性能が目標に達しない場合は、再検討となる。

# 3. MOSFET の特性

キーコンポーネントである増幅素子の理解は、設計を有効かつ効率的に行うために不可欠である。ここでは、増幅素子の代表として MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor)を取り上げトランジスタの増幅特性について理解を深める。

# 3.1 動作原理

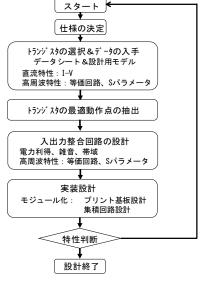

図3にnMOSトランジスタの構造を示す。その動作はゲートに正電圧Vgを印加するとゲート酸化膜直下に負の電子が集まる。ドレイン・ソース間にVdを印加し水平方向に電界を発生させると電流が流れる仕組みで、ゲート電圧Vg(垂直方向の電界)を制御することにより、出力電流を制御できる。増幅動作を可能としているのは、垂直方向の電界で、水平方向の電流を制御している点にある。ゲート端子は、電界を発生させているだけなので少ない電力でドレイン・ソース間を流れる電子の量を制御でき 1 より大きい増幅率 $\mu$ (後述)が得られる。ゲート幅をより広くとれば、より多くの電子を集めることができ、大電流を制御できることになる。

## 3.2 直流特性 (電圧電流特性)

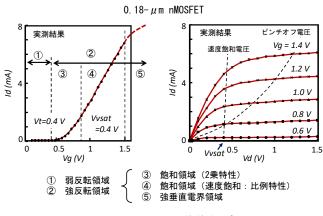

MOSFET の動作領域は、図4に示す領域に分けられ、増幅回路では主に飽和領域(2乗特性と速度飽和領域)を利用する。その時のドレイン電流 Id は、下式で表される。

① 2 乗特性領域:  $V_g$ - $V_t$ < $V_{vsat}$ , $V_{vsat}$ < $V_d$

$$I_d = K_T \cdot W_q \cdot (V_q - V_t)^2 (1 + \lambda \cdot V_d) \tag{1}$$

② 電子またはホールの速度飽和領域:  $V_{vsat} \leq V_{g} V_{t}, V_{d} V_{g} V_{t} \leq V_{d}$

図3 nMOSFET の構造

図 4 MOSFET の動作領域

$$I_d = K_T \cdot W_g \cdot \left\{ \left( V_g - V_t \right) \cdot V_{vsat} - \frac{1}{2} V_{vsat}^2 \right\} (1 + \lambda \cdot V_d)$$

(2)

ここで、 $K_T$ : ドレイン電流係数、Wg: ゲート幅、Vt: しきい値電圧、 $\lambda$ : ドレイン変調係数、Vvsat: 電子またはホールの速度飽和電圧(速度飽和電界 x ゲート長 Lg)である。

速度飽和領域はゲート長がサブミクロン以下の MOSFET で顕著となる。この領域の Id は Vg に比例 し 2 乗特性は示さない。

# 3.3 MOSFET の増幅素子 3 定数

入力信号電圧の変化を $\Delta V_g$ 、出力信号電圧の変化を $\Delta V_d$ とすると、出力電流変化 $\Delta I_d$ は、

$$\Delta I_d = \frac{1}{r_0} \Delta V_d + g_{m} \Delta V_g \tag{3}$$

と表現できる。ここで、 $g_m$  は相互コンダクタンス、 $r_o$ は出力抵抗で、それぞれ下式により得られる。

$$g_m = \frac{\partial I_d}{\partial V_g} \tag{4}$$

$$r_o = \frac{\partial V_d}{\partial V_a} \tag{5}$$

図1のトランジスタ部の電圧利得 $G_v$ は、負荷を $Z_L$ とすると、

$$G_v = -g_m \cdot (Z_L //r_o) \tag{6}$$

で与えられる。マイナスは反転増幅を示す。ここで、 $Z_L$ が無限大の時の $G_v$ の絶対値は増幅素子の増幅能力を示す増幅率 $\mu$ と呼ばれている[6]。

$$\mu = g_m \cdot r_o \tag{7}$$

仮に負荷  $Z_L$  を LC 並列共振回路で構成すると共振周波数でのインピーダンスは理想的には無限大となり、その時の利得は増幅率  $\mu$  の最大値となる。

gm, ro,  $\mu$  は、増幅素子の三定数と呼ばれ、3 極真空管の発明以来、増幅回路設計時の基準となる増幅素子の定数として用いられている。増幅素子としての条件は、 $\mu$  が 1 より大きく、また、その値が大きい程、増幅能力が高いことを示す。

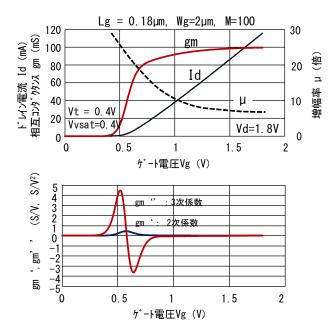

(4,5,7)式から MOSFET の 3 定数を考えると、相互コンダクタンス  $g_m$ は、2 乗特性領域で、

$$g_m = 2K \cdot W_g \cdot (V_g - V_t) \tag{8}$$

となる。さらに $V_g$ が高くなると速度飽和領域に入り、

$$g_m = K \cdot W_g \cdot V_{vsat} \tag{9}$$

となり、 $g_m$ は  $V_g$ に依存せず一定の値を取る。

相互コンダクタンスは、図5に示すように2乗特性領域で増加し、速度飽和領域で一定値に飽和する。

次に出力抵抗  $r_o$  を導出し増幅率  $\mu$  を求めると、2 乗特性領域では、

$$\mu = \frac{2}{\lambda \cdot (v_g - v_t)} \tag{10}$$

速度飽和領域では、

$$\mu = \frac{1}{\lambda \cdot \{(V_g - V_t) - \frac{1}{2} V_{vsat}\}}$$

(11)

となる。いずれも $\mu$ はドレイン変調係数 $\lambda$ と $V_g$ により制限される。

$g_m$  と  $\mu$  の関係は、図 5 のシミュレーション結果からも分かるように  $V_g$  を高くしていくと  $g_m$  は増加するが  $\mu$  は低下する。

また、 $g_m$  は(8,9)式から分かるようにゲート幅  $W_g$  を大きくすれば、大きな値を得ることができるが、 $\mu$  には  $W_g$  依存性がない。 $W_g$  を大きくすることにより  $I_d$  が増し、 $g_m$  は大きくなるが、逆に  $r_o$  は  $W_g$  に反比例 するため、 $\mu$  はトランジスタ固有の値となる。利得を得るために  $g_m$  を大きくしても最大利得は、 $\mu$  により制限される。

なお、集積回路に用いられている MOSFET では製造技術の微細化(ゲート長  $L_g$  および酸化膜厚  $t_{ox}$ )により  $K_T$  値を高め、電流駆動能力の向上によりデジタル回路の高集積化、高速動作化を可能にしてきた。しかし、耐圧は低下し $\lambda$  の値は増加、その結果  $\mu$  値は低くなっている。このため  $L_g$  の小さい先端的なMOSFET は高周波特性に優れるが目的とする増幅回路に適さない場合があるので注意が必要である。

図5 MOSFET の相互コンダクタンス、 増幅率、歪係数

#### 3.4 動作点による歪係数

増幅回路設計では、所望の電流出力が得られる動作点(ゲートとドレインのバイアス電圧)を設定する。ゲートバイアスの設定は、前述の直流特性、 $g_m$ と $\mu$ のトレードオフ関係、および、非線形特性を考慮して設定する。

$g_m$  は、図 5 から分かるように  $V_g$  の変化に対して線形ではない。 $g_m$  の 2 次、3 次の微分係数を用いると  $\Delta I_d$  は下式で表現できる。

$$\Delta I_d = g_m \cdot \Delta V_q + g_m \cdot \left(\Delta V_q\right)^2 + g_m^{\text{in}} \cdot \left(\Delta V_q\right)^3 \tag{12}$$

ここで図5の相互コンダクタンス特性を微分して2次、3次の係数の変化を求めると図5の下段の特性を示す。2次係数値は2乗特性領域で、3次係数値は弱反転と2乗特性、および2乗特性と速度飽和の各領域の境界で高くなる。歪の少ない増幅動作を得るには、これらの領域を避けてゲートバイアス電圧を設定する。図5の場合、ゲートバイアス $V_g$ を1Vに設定すると歪の少ない線形動作が可能となり、その時の増幅率 $\mu$ は10倍となる。最大20dBの電圧利得が期待できることになる。低歪特性よりも高い小信号利得を優先するのであれば、増幅率 $\mu$ の大きい領域を利用する。 $V_g$ をしきい値電圧より少し高めに設定すれば良い。

以上のように動作点は、目標達成に必要な出力電流や増幅率、歪特性を念頭に設定する。

#### 3.5 高周波特性

MOSFET の高周波特性は、ゲート容量、出力抵抗および端子電極に付随する寄生抵抗成分により制限される。

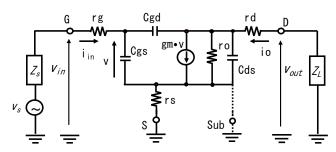

# (1) MOSFET の等価回路

高周波特性を MOSFET の等価回路から考える。等価回路は図3の構造から容易に求めることができる。図6にソース接地増幅回路の小信号等価回路(π型等価回路)を示す。

# (2) 電圧利得の周波数特性

信号伝達特性として電圧利得 $G_v$ を、この等価回路から求めると、

$$G_v = \frac{v_{out}}{v_{in}} = -\frac{g_m \cdot R_L}{1 + g_m \cdot r_s} \times G_i(\omega) \times G_o(\omega)$$

(13)

$$G_i(\omega) = \left(\frac{1}{1 + j\omega in \frac{r_g + r_s}{1 + dm r_s}}\right) \tag{14}$$

$$G_o(\omega) = \left(\frac{1}{1 + j\omega C_{ds} \cdot Z_L}\right) \tag{15}$$

$$C_{in} = Cgs + Cgd(1 + \frac{g_m \cdot Z_L}{1 + g_m \cdot r_s}) \qquad (16)$$

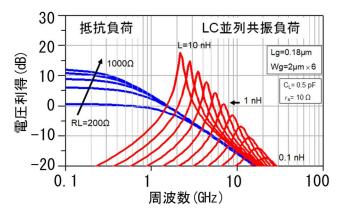

となる。MOSFET の周波数応答は抵抗負荷( $Z_i=R_L$ )を想定すると入力側と出力側の2つの RC 時定によるローパスフィルタ特性となっている。入力側の $G_i(\omega)$ と出力側の $G_o(\omega)$ のどちらが先に動作帯域を制限するかは素子値に依存するが、 $R_L$ の値が大きい程、 $G_o(\omega)$ が支配的になる。

インダクタ L と容量 C の並列共振回路を負荷に用いた場合は、共振容量に FET の出力容量を取り込むことができ、より高い周波数領域での増幅動作が可能となる。図 7 に抵抗負荷と LC 共振負荷の場合の利得の周波数特性例を示す。抵抗負荷では、増幅率μよりも低い値となるが、LC 共振負荷では、増幅率μを最大限に活かすことができるため、抵抗負荷よりも高利得でしかも高周波での動作が可能となる。

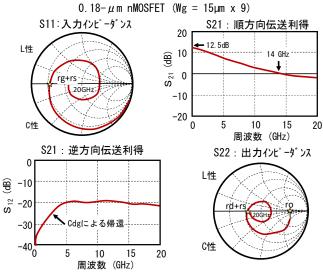

# (3) Sパラメータによる周波数特性

# a. Sパラメータ

市販のトランジスタを用いる場合、2 ポートのS パラメータをもとに設計に着手することが多い。4 つのSパラメータは、

S<sub>II</sub>:入力反射係数(入力インピーダンス特性)

S12: 逆方向伝送係数 (アイソレーション特性)

S21: 順方向伝送係数(利得特性)

S22:出力反射係数(出力インピーダンス)

図6 MOSFET の小信号 π型等価回路

図7 電圧利得の周波数特性 (ソース接地)

図8 MOSFET のSパラメータ (実測)

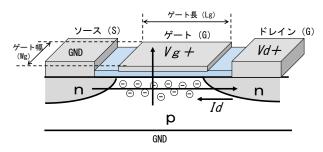

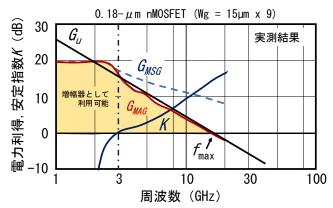

### b. 最大電力利得の周波数特性[8,9]

Sパラメータの  $S_{21}$ は、 $50\Omega$ 負荷時の電圧利得に相当し、その絶対値の 2 乗  $|S_{21}|^2$  は、トランスデューサ電力利得  $G_T$  (Transducer Power Gain) と呼ばれる。また、電力の一部は入出力で反射されるので $S_{11}$ 、 $S_{22}$  の影響を考慮し、 $S_{12}$  は十分小さく無視できとすると、下記の電力利得式を得ることができる。

$$G_{u} = G_{s} \times G_{Tr} \times G_{L}$$

$$= \frac{1 - |\Gamma_{s}|^{2}}{|1 - S_{11} \cdot \Gamma_{s}|^{2}} \cdot |S_{21}|^{2} \cdot \frac{1 - |\Gamma_{L}|^{2}}{|1 - S_{22} \cdot \Gamma_{L}|^{2}}$$

(17)

ここで、 $\Gamma_s$ 、 $\Gamma_L$  は信号源および負荷との反射係数(インピーダンスと等価)である(図 10 参照)。これを単方向電力利得(Unilateral Power Gain)と呼び、この式においてトランジスタの入出力インピーダンスと共役整合を取とると( $\Gamma_s$ = $S_{II}$ \*、 $\Gamma_L$ = $S_{22}$ \*)、最大電力利得になる。

$$G_{u\_max} = \frac{|S_{21}|^2}{(1-|S_{11}|^2)\cdot(1-|S_{22}|^2)}$$

(18)

但し、 $S_{12}$ が無視できるほど小さい場合である。実デバイスでは、図6の等価回路から分かるように  $C_{gd}$  の影響により、高周波では出力信号が入力に帰還する双方向動作となる。信号源  $Z_s$ のインピーダンスを高くすると、 $C_{gd}$ の影響が大きくなり動作が不安定になることは容易に推定できる。そこで、動作安定条件を考慮した時の最大電力利得式が導出されている。最大有能電力  $G_{MAG}$  (Maximum Available Power Gain)と呼ばれる。

$$G_{MAG} = \frac{|S_{21}|}{|S_{12}|} (K + \sqrt{K^2 - 1})$$

(19)

$$K = \frac{1 - |S_{11}|^2 - |S_{22}|^2 + |S_{11}S_{22} - S_{12}S_{21}|^2}{2|S_{12}||S_{21}|}$$

(20)

K は安定指数(Stability factor K)で、K>1 で絶対 安定となる。どのようなパッシブの複素インピーダンスを入出力に接続しても安定に動作する条件で ある。K<1 の場合は、インピーダンス条件により動作が不安定になり、最悪、発振を生じることになる。また、K=1 の時の境界条件時の利得を最大安定利得  $G_{MSG}$ (Maximum Stable Gain)と呼んでいる。

各電力式による周波数特性を図9に示す。GMAG、GMSG 以下の領域が増幅回路として利用可能な領域である。

なお、Kの値が 1 より小さい低周波領域では、  $|S_{11}| = |S_{22}| = 1$ 、 $S_{12} = 0$  になり、Kの値は 0 に 近づくが、すべてのインピーダンスに対して不安定 になるわけではない。安定動作となるインピーダンス領域を見極める必要があるが、増幅回路として利用可能である。また、K>1 となる周波数領域の使用 は安心ではあるが実現できる最大利得は低くなる。

図9 電力利得と安定指数の周波数特性

# (4) 高周波特性指標

図 9 において、電力利得が 0dB (1 倍) となる周波数を最大発振可能周波数  $f_{max}$  と呼んでいる。この値が高い程、高周波動作が可能となる。図 6 の等価回路から  $f_{max}$  を求めると、

$$f_{max} = \sqrt{\frac{f_T}{8\pi C_{gd} r_g}}$$

(21)

となる。ここで、 $f_1$ は高域遮断周波数と呼ばれ、電流利得が $f_2$ 0dB (1倍) となる周波数である。

$$f_T = \frac{g_m}{2\pi (C_{qs} + C_{ds})} \tag{22}$$

これは、相互コンダクタンスと入力容量の比である。 $f_{\text{T}}$ 、 $f_{\text{max}}$  は増幅回路を設計する際に、使用するトランジスタを選定する際の目安となる。増幅回路の場合、 $f_{\text{max}}$  を参考にする。 $f_{\text{T}}$  はデジタル回路の目安として用いられている。トランジスタの選定にあたっては、大雑把ではあるが、実現したい利得と周波数の積が上記の指標値よりも低ければ、実現可能な領域と判断できる。

# (5)トランジスタ特性の測定

設計用データがない場合は、測定を行うことになる。トランジスタ電圧電流特性は、DC電源を用いれば容易に測定できる。高周波特性は、ネットワークアナライザでSパラメータを測定することにより把握できる。 $S_{21}$ は伝送特性を示し、 $S_{11}$ 、 $S_{22}$ からは、入出力インピーダンスの様子を把握でき、そのデータから等価回路パラメータも求めることができる。 $f_{T}$ ,  $f_{max}$  は、測定したSパラメータをマトリクス変換し、 $f_{T}$  は  $H_{21}$ 、 $f_{max}$  は単方向電力利得の周波数特性を計算し求めることができる。

#### 4. バイアス回路

トランジスタを所望の特性で動作させるために は、(3.3),(3.4)節で述べた様にトランジスタを最 適な動作点 (ゲート電圧、ドレイン電圧) に設定す る必要がある。バイアス電圧をトランジスタに印加 する回路をバイアス回路と呼ぶ、図1の回路では、 R<sub>i</sub>とL<sub>n</sub>がバイアス回路である。動作周波数において、 インピーダンスの低い電圧源に信号が流れ込まな いように、インピーダンスの高い抵抗、インダクタ を用いる。図1の回路では、電源電圧 1/2を、チョー クインダクタを介してドレイン端子に印加し、ゲー ト端子には直流電流は流れないので高抵抗の R<sub>i</sub>を 介して印加している。ゲートバイアス電圧 Vbias は、 電源電圧を抵抗で分圧して用いることが多い。なお、 電源端子は高周波 GND を強固にし、動作を安定化さ せるため、必ず Vp と Common GND間にバイパスコン デンサ(動作周波数に対してインピーダンスを十分 低くする大容量)を付加する。

また、図1における  $C_c$ は、高周波信号のみを通過させ、直流をカットする容量である。高周波システムでは、GND を基準に信号を伝送している。直接接続すると、ゲート端子、ドレイン端子が GND と短絡してしまい、バイアス電圧を印加できなくなってしまうので、注意が必要である。

なお、5GHz 以上の高周波帯ではバイアス設定用の素子として分布定数素子(図 13)の利用することが多い。

#### 5. 整合回路の設計

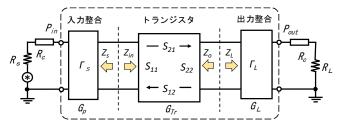

整合回路設計はマイクロ波増幅器設計の要である。整合設計を考えるにあたって改めて、Sパラメータによるマイクロ波増幅器の構成を図10に示す。

# 5.1 整合回路の重要性

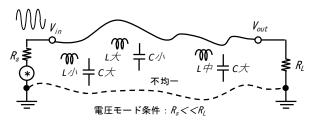

### (1) 伝送線路インピーダンスとの整合 [10]

低周波回路における信号の入出力は、単に配線を接続すればよいが、信号の波長が配線長に近づき、さらに短くなってくると、信号が配線の上を伝搬するようになる。図 11(a)に示すように不安定な配線のインダクタンス成分や容量成分の影響を受け信号 歪や減衰を生じる。

同軸ケーブルやプリント基板配線で使用するストリップラインは、信号線と GND 間の距離を一定に保ち高周波信号を高品質のまま伝送できるよう構成されている。図 11(b)において、波形品質を維持する条件は、送信端の信号源の抵抗値  $R_s$  と伝送線路のインピーダンス  $R_c$  (特性インピーダンスとよび実数値を取る)、受信端の抵抗値  $R_t$  を一致させる。これを、「整

図10 Sパラメータ表現によるマイクロ波増幅器

(a) 低周波の信号伝送 (電圧モード)

(b) 高周波の信号伝送(電力モード)

図 11 低周波と高周波の信号伝

合を取る」と言い、マイクロ波増幅器における入出力部の整合回路は、伝送線路インピーダンスと整合を取るために付加し高周波の信号の入出力を可能にしているのである。現在の高周波の通信システムや計測システムでは、信号伝送に  $R_c=50\Omega$  または  $75\Omega$  の伝送線路が用いられているので、これらの値と具体的に整合を取る。

# (2)トランジスタに作用する信号源インピーダンスと 負荷インピーダンスとの整合

トランジスタによる増幅動作は、先に示した単方向電力利得の式(17)から分かるようにトランジスタ側から見た整合回路のインピーダンスに依存し、利得や周波数特性が変化する。負荷インピーダンスと信号源インピーダンスがトランジスタに作用し、マイクロ波増幅器の特性を決定づける。マイクロ波増幅器設計の最大のポイントである。

#### 5.2 整合回路設計の考え方 [8,9]

Sパラメータの入出力インピーダンスと共役整合(複素インピーダンスに対する整合条件)をとると電力利得が最大になることを式(18)に示した。

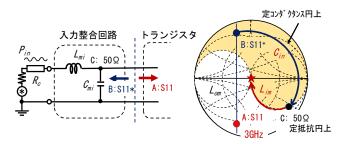

例としてSパラメータの入力インピーダンス ( $S_{II}$ ) との整合を考えてみる。整合回路は、2つのパッシブ素子で実現できる。整合インピーダンスは計算で

求められるが、スミスのインピーダンスチャート上の定抵抗円とコンダクタンスチャートの定コンダクタンス円を組み合わせによる考え方、導出が便利である。図 12 に整合の取り方を示す。図8 の8 パラメータデータ3GHz時の $S_{II}$ のA点と整合を取る。共役インピーダンスは、上下対象点に位置するので、12 展点が求まる。入力端子と並列に容量を接続し、容量を増やし定コンダクタンス円上を右へ回転させる。12 の定抵抗円上の12 に達した値を12 になっる。次に12 に変した値を13 に表した値を13 になって、中心の14 になった。

図 12 の場合、 $L_{mi}$  と  $C_{m}$  を入れ換えても整合を確保できる。整合のコツは、容量を並列に接続するときは右回転、直列の時は左回転、インダクタの場合は逆に並列に接続するときは左回転、直列の時は右回転なること利用することである。この手法により任意のインピーダンスと  $50\Omega$  の整合を取ることが可能となる。出力側も同様の考え方で整合が可能である。整合を取るインピーダンス点をずらすと式(17)から分かるように利得は、減少することになる。

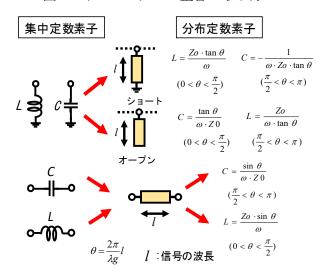

整合用の素子は図 13 に示すように集中定数素子を分布定数素子へ置き換えることも可能である。 5GHz を超える高周波では精度が得られる分布定数素子を用いることが多い。

なお、動作帯域が広帯域に渡る場合は、複数のLC 回路の組み合わせや抵抗を利用する場合もある。

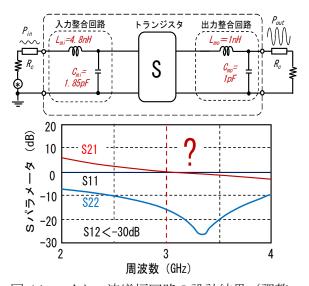

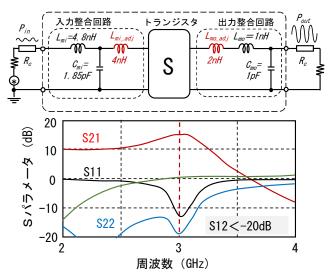

# 5.3 マイクロ波増幅回路の設計事例

以上の手法により図8で示したSパラメータを用いた3GHzの増幅回路の設計解析結果を図14に示す。5.2項で述べた手法によりLC回路の定数を決定したが、残念ながら $S_{11}$ は全く整合が取れていない。 $S_{21}$ 利得も0dB@3GHz である。 $S_{22}$ の整合点も高周波側へシフトしている。

この原因は、 $S_{12}$ の影響である。具体的には、図6の等価回路  $C_{dg}$  の影響により入力側と出力側のインピーダンスを独立に決定できないことによる。特に図6の等価回路の入力容量  $C_{in}$  は、式(16)から分かるように、 $C_{dg}$  が増幅動作で利得倍されるミラー効果により入力インピーダンスが変化してしまう。

この影響をキャンセルするため、 $C_{im}$  の値を低減し、削除も試みたが整合を確保できなかった。 $L_{im}$  の値を調整しても上手くいかない。

そこで、5.2 項で求めた定数値は、そのままにして置き、 $C_{in}$  増加の影響を新たなインダクタ  $L_{im\_adj}$ でキャンセルすることとした。改善回路の解析結果を図 15 に示す。 $L_{im\_adj}$ の付加により特性は改善した。出力側の整合も入力側のインピーダンスに依存し

図 12 インピーダンス整合の取り方

図 13 集中定数素子と分布定数

図 14 マイクロ波増幅回路の設計結果 (調整

て変化するので、負荷側にも調整用の  $L_{om\_adj}$  を追加 ( $L_{omj}$  値を大きく) した。最終的な値は、 $L_{im\_adj}$  と  $L_{om\_adj}$  の値を交互に変え周波数特性を確認しながら 特性を追い込む。図 15 の S パラメータは、その作業の結果である。 $S_{21}$  利得は、図 9 の  $G_{MAG}$  の値とほぼ一致する 16 dB を得た。整合性は入出力とも-10 dB 以下である。増幅回路としての安定指数 K は 3GHz で 1 (0dB)よりも大きい値が得られている。

マイクロ波増幅回路の設計、評価では、ロードプル法と呼ばれる手法が提案され用いられている。信号源と負荷の両方のインピーダンスを網羅的に変化させ、最適なインピーダンス条件を決定する。前述の通り Cdg の影響により 5.2 項の手法のみでは、最適化が難しいための対処的な手法である。

なお、図 15 のトランジスタ部分に図 6 の等価回路を当てはめて考えて見ると、マイクロ波増幅器は、相互コンダクタンスを挟み込んだフィルタ回路と認識できる。フィルタ回路として定数を最適化する設計手法も考えられる。

# 6. 無線通信用マイクロ波増幅器

マイクロ波増幅器は無線通信システムで多く利用されている。送信部では電力増幅器が、受信部では低雑音増幅回路が不可欠である。

# 6.1 電力増幅器

無線信号送信用電力増幅器は、アンテナから情報の載った電磁波エネルギー信号を空間へ放射するための増幅器である。アンテナが負荷となり、そのインピーダンス  $(50\Omega$ または  $75\Omega$ ) にエネルギー (電力) 信号を供給する。

#### (1) 負荷への大電力供給

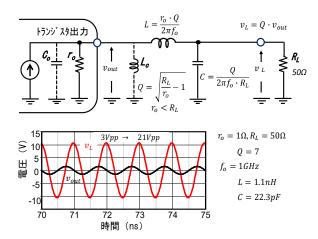

具体的に MOSFET で 1 W の信号電力をアンテナへ供給するには、どうすればよいであろうか。 $50\Omega$  の負荷に 1 W の電力を直接供給するには、20 Vpp の電圧信号を負荷に印加する必要がある。ここで、0.18- $\mu$ m MOSFET を増幅素子として選択すると、許容できる電源耐圧は 3.5 V 程であるので、20 Vpp の電圧信号を負荷へ直接供給することはできない。そこで、整合回路のインピーダンス変換特性を利用する。トランジスタ出力の負荷抵抗値として  $1\Omega$  を想定すると、電圧は 2.83V まで低減できることになる。勿論、供給電流は、2.83A と大電流になるが、多数の FET を並列接続すれば実現可能である。総ゲート幅が 1 mm を超える MOSFET が電力出力用として用いられている。

図 16 に整合回路による電圧振幅の変換回路例を示す。まず、周波数  $f_o$ でトランジスタの出力容量  $C_o$ をインダクタ  $L_c$ との並列共振によりキャンセルする。図中の条件式から、トランジスタの出力抵抗が  $1\Omega$ で、周波数  $f_o$ が 1GHz 時、L の値を 1.1nH、Cを 22.3pF とすると 7 倍(Q 値)の電圧振幅が得られる。これにより 3 Vpp の電圧信号が、21 Vpp に変換される。このような電圧振幅変換回路を用いることにより、低耐圧の MOSFET でも  $50\Omega$  負荷への大

図 15 マイクロ波増幅回路の設計結果 (調整後)

図 16 整合回路による電圧信号振幅変換電力信号の供給が可能になる。

#### (2) 電力効率

電力増幅回路の電力効率 $\eta$  (%) は出力電力 $P_{out}$  と供給した直流電力 $P_{in\_dc}$  に比により定義される。数値としては高い方が良い。

$$\eta = \frac{P_{out}}{P_{in,dc}} \times 100 \tag{23}$$

また、増幅回路の電力利得を考慮した付加電力効率 PAE (Power-added efficiency) も性能評価パラメータ として用いられている。

$$PAE = \frac{P_{out} - Pin}{P_{in\_dc}} \times 100 \tag{24}$$

PAE は増幅回路の利得が十分高い場合は、ηとほぼ一致するが、利得が低いと駆動に要する電力が必要になることから、その分効率が低くなり駆動に電力が必要となることを含めた定義となっている。

#### (3) 高電力効率化

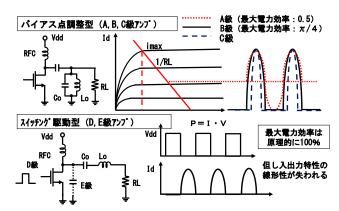

電力効率は、図 17 に示すように動作バイアス点調整やパルス信号駆動により高効率化できる。

### ① A,B,C級:バイアス点調整型

B級は半波動作、C級さらに動作点を下げ、アナログ信号入力をパルス信号入力動作に近づけることにより電力効率を改善している。線形動作のA級の最大電力効率は、50%であるが、B級では78.5%、C級では、それ以上の値が原理的に得られる。

# ② D、E級:スイッチング駆動型

D級はパルス信号入力でトランジスタをスイッチングする構成である。出力電流と電圧は交互に切り替わることから瞬間的に切り替われば電力を消費せず、100%の効率が得られるはずである。実際は出力波形の立ち上がり/立下りがなまり、スイッチング時に電力を消費してしまう。そこで出力に容量を並列に付加しその充放電特性を利用して電流の立ち上がり/立下り時間を改善する構成が E級である。その他、B級バイアスで分布定数素子を負荷に加えた F級などもある。

効率の改善は、出力波形歪を生じるため、導入にあたっては電力効率と線形特性とのトレードオフを考慮する必要がある。無線通信では、線形性に優れるAB級の電力増幅器が多く使用されている。

#### 6.2 低雑音増幅器

無線信号受信用低雑音増幅器は、アンテナで受信した微弱な信号を増幅する。このため、高利得で低雑音な特性が要求される。

### (1) 雑音整合

MOSFET の高周波動作時の雑音要因は、ドレイン電流によるチャネル雑音と寄生抵抗成分(図6の $r_g$ ,  $r_s$ ,  $r_d$ )による熱雑音である。このため、寄生抵抗成分が小さい FET を用い、利得とのトレードオフを考慮しながらバイアス電流は少なめに設定し用いる。

また、雑音指数 NF は値が最小となる信号源インピーダンス点(複素アドミタンスで表現することが多い)を有する。NF 値が最小になるように信号源インピーダンスを設定することが雑音整合である。

但し、この信号源インピーダンス点は、先に述べた最大電力利得時のインピーダンス条件と一致しない。NF 値が最小になるように設定すると利得が低下する。利得と雑音のトレードオフを考慮し、信号源インピーダンスを最適化することが低雑音増幅器設計のポイントである。

なお、負荷インピーダンスによる NF への影響は 小さい。

図 17 マイクロ波増幅器の高電力効率化

#### 7. おわりに

マイクロ波増幅器設計の基本的考え方をトランジスタ1段の回路を例に概説した。設計のポイントはトランジスタ特性の理解と整合設計の考え方にある。現在は集積回路化の時代であるのでトランジスタ部分は、高機能な集積回路に置き換えて同様に考えることができる。

原理原則を考えることが設計力の向上とその応 用範囲の拡大につながる。本稿が回路設計の本質を 追求し、これからの時代を切り開く若い研究開発者 の皆さんに少しでも参考になれば幸いである。

#### 文 献

- [1] T. H. lee," The Design of CMOS Radio-Frequency Integrated Circuits, second edition", Cambridge university press, 2004, ISBN 0-521-83539-9.

- [2] W. Brinkman," The Transistor: 50 Glorious Years and Where We Are Going", Digest of IEEE International Solid-State Circuit Conference (ISSCC 1997), Session 1.2, pp.22-26, February 1997.

- [3] A. A. Abidi, "RF CMOS Comes of Age," IEEE J. Solid-State Circuits, vol. 39, pp. 549–561, April 2004.

- [4] Noboru ISHIHARA, Shuhei AMAKAWA, Kazuya MASU, "RF CMOS Integrated Circuit: History, Current Status and Future Prospects", IEICE TRANSACTIONS on Fundamentals of Electronics, Communications and Computer Science, Vol. E94-A, No. 2, pp. 556-567, Feb 2011.

- [5] Chun Wang et.al," A 22.7dB Three-stage D-band Power Amplifier in 65nm CMOS," 2019 年電子情報通信学会エレクトロニクスソサイエティ大会, c-12-32, 2019.

- [6] 中村 欽雄, 詳解電子回路, 東京電機大出版局, 1975.

- [7] N. Ishihara and T. Shimizu, "A Simple Equation Model for RF MOS FET," SiRF06, pp.93-96, San Diego (USA), Jan 2006.

- [8] Ralph S. Carson," High-Frequency Amplifiers", A Willey International Publication, 1975, ISBN 0-471-13705-7.

- [9] Guillermo Gonzalez, "Microwave Transistor Amplifiers, Analysis and Design, Second Edition", Prentice Hall, 1997, ISBN 0-13-254335-4.

- [10] 石原 昇, "高速デジタル信号伝送技術とその評価の基礎 "APMC 2010 基礎講座テキスト, pp.41-50, December, 2010.