# 移動通信用復調信号処理の基礎

# Foundation of Demodulation Signal Processing for Mobile Terminals

向井 学 三ツ木 淳

Manabu MUKAI Jun MITSUGI

株式会社東芝 研究開発センター モバイル通信ラボラトリー

Mobile Communication Laboratory, Corporate Research & Development Center, Toshiba Corporation

1, Komukai-Toshiba-cho, Saiwai-ku, Kawasaki, Kanagawa, 212-8582 Japan

Tel: +81-44-549-2433, Fax: +81-44-520-1806, mukai@csl.rdc.toshiba.co.jp

**あらまし** ここでは、無線通信システムにおける信号処理の基礎について、W-CDMA モデム、無線 LAN モデムにおける受信信号処理を規格仕様と対比しながら解説する. また、W-CDMA をモチーフとしたモデムアーキテクチャ検討結果について紹介する.

#### 1. まえがき

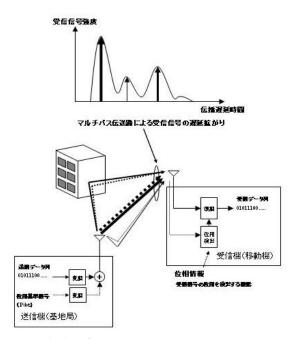

移動通信システムでは、伝送路上で加わる干渉やノイズの他、図1に示す様な反射波によるマルチパス伝播環境や、移動に伴うドップラー変動に対応した技術が要求される。ディジタル変調を用いたシステムの復調器では、伝播路においてこれらの擾乱を受けた受信信号に対して処理を施し、送信データを正確に復調する必要がある。そのためにまず、受信した信号に対しAGC/AFC/クロック同期を掛けディジタル信号処理が容易な状態にする。さらに、受信信号から信号フォーマットやフレーム/スロットタイミングを読み取るシステム同期の処理を施し、位相や振幅の基準情報を用いて復調処理を行う。

携帯端末においてバッテリーの持続時間を向上させるためには上記の一連の過程を極力短い時間で処理する必要が有り、通常これらの過程をスムーズに行うためのシステム的工夫がなされている。本稿では、近年サービスが普及しているW-CDMAシステム、無線LANシステムにおける復調信号処理についてシステム的な差異を比較しながら解説する。

まず2章において無線LANの規格の一つであるIEEE802.11aシステムについて、システム概要、復調処理の原理、受信機基本構成を述べ、受信性能を向上させるための工夫の一手法を紹介する.次に3章においてセルラーシステムの1規格である3GPPDS-FDDモード(W-CDMAシステム)について、システム概要、復調処理、受信機構成、受信性能向上の手法を紹介する.4章においては、モデム設計において注意すべき点であるハードウエアとソフトウエアの機能切り分けに対する検討結果の紹介を行う.

図1 移動通信システムにおけるマルチパス 伝播環境

## 2. 無線 LAN モデムの構成と課題

### 2.1 無線 LAN (IEEE802.11a) システム[1]

IEEE802.11aは5GHz帯のバンドを使用した無線LANシステムで、最大54Mbpsのデータレートを実現する.このシステムは、元々最大伝送速度2 MbpsのIEEE802.11を高速化させたものであるが、同様にIEEE802.11を高速化させたIEEE802.11bとは使用するバンドも変調方式も異なる.なお、IEEE802.11bとの互換性を持ちつつ高速化を実現するシステムがIEEE802.11gであり、IEEE802.11bと同様に2.4GHz帯のISMバンドを使用し、IEEE802.11bモードと54 Mbpsの0FDM 信号で通信ができる.

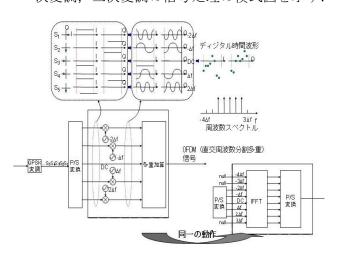

IEEE802.11aは一次変調方式にBPSK~64QAMの

ディジタル変調を、また二次変調方式にOFDM(直交周波数分割多重)方式を採用し、通信品質要求に応じて一次変調方式と誤り訂正符号の符号化率を変える構成となっている。図2にOFDM信号の一次変調、二次変調の信号処理の模式図を示す。

#### 図2 OFDM 信号変調器における信号処理

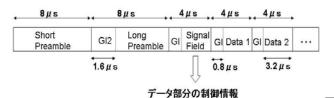

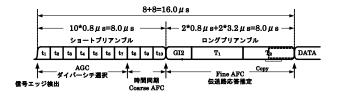

無線LANシステムは、伝送すべきデータが発生した時点でデータを伝送するパケット通信方式であり、パケット単位に復調に必要な付加シンボル、制御情報が包含されている。図3にIEEE802.

11aシステムのパケットフォーマットを示す. 図の様にパケット先頭にOFDMシンボル同期,パケット同期に必要なプリアンブル部を持ち,パケット受信毎に同期をかける.送信データはプリアンブル,シグナルフィールドの後に附加され,ロングプリアンブルで測定した基準位相,振幅を用いて復調を行う.

図3 IEEE802.11a システムのパケット構成

## **2.2 IEEE802.11a** システムの受信信号処理と 受信機構成

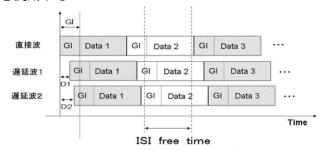

IEEE802.11a システムで用いられている OFDM 変調を実施するために,変調器は IFFT を行い周 波数軸上でかけた変調を時間軸波形に変換して送信する. 復調器ではその逆の処理の FFT を施し復調を行うが,この処理を行うために FFT ウインドウのタイミングを決定する必要がある. IEEE802.11a ではマルチパス耐性を向上させるために,図4に示す様にデータの変調を行った信号の一部を繰り返して延長させるガードインターバルを設けている.これにより,マルチパ

ス伝播環境で遅延した前後の変調信号のシンボル間干渉を受けない復調タイミングを得ることができ、FFT ウインドウの決定はこの復調タイミングの決定を意味している。このタイミング決定は、パケット先頭のショートプリアンブルを使用する。

D1、D2 < GI ならば 符号間干渉のないFFTウィンドウが存在

図4 OFDM シンボルガードインターバルによるマルチパス耐性向上

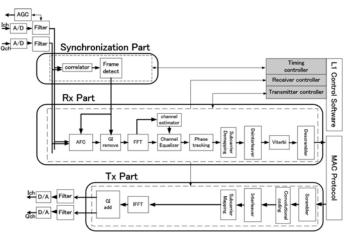

図5に示した機能ブロック図は, IEEE802.11a システムにおける変復調処理を実現するための モデム構成例である. 受信処理系は大きく同期 部と受信処理部に分割され、同期部では前述の パケット, FFT ウインドウのタイミング決定を 行い、この情報を基にして受信処理部での処理 を行う. 同期部ではショートプリアンブルを用 いて信号エッジ検出, AGC, 粗同期, 時間同期の 処理を行う. 受信処理部では、粗同期のかかっ た受信信号に AFC 処理を施し、同期部から得ら れたタイミングに応じてガードインターバル分 の信号を除去し FFT 処理を施す. FFT 処理後の 信号はプリアンブル信号とそれ以降の変調信号 に応じて2分割されるが、まずロングプリアン ブル信号を使用して正確な周波数同期と伝送路 応答推定を行う.次に、伝送路応答推定結果を 基に等化,復調処理を行い、さらにデインター リーブ、チャネルデコーディング、デスクラン ブルを行い MAC 部に復調後のデータを受け渡す.

図5 無線 LAN モデム部機能ブロック図

#### 2.3 無線 LAN 受信機における技術課題

2.2 で述べた IEEE802.11a 受信機において,アナログ部補正, AGC, AFC, タイミング同期, 伝送路応答推定などの処理は受信性能に係り,様々な検討がなされている[2]-[10].特に同期, 伝送路応答推定については OFDM 信号の復調に直接関係しており,本稿ではその中でも伝送路応答推定のノイズ耐性向上の一手法に対する検討結果を紹介する[11].

#### 図 6 IEEE802.11a パケットプリアンブル部

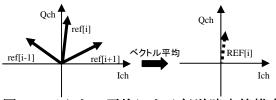

IEEE802.11a では既知信号であるロングプリ アンブル部 (図6) を使用して伝送路応答推定 を行いその推定結果からデータ部を復調するた め、伝送路応答推定値の精度が受信特性に大き く影響する. 本提案方式では、ロングプリアン ブル部から推定された伝送路応答値に振幅と位 相を別々にフィルタリングすることで、ノイズ 環境下での推定精度を向上させる. ここで, 位 相,振幅を個別にフィルタリングする理由は以 下の通りである. 受信処理時の各サブキャリア 間の位相差は、同期処理時の FFT ウインドウの 位置に応じて異なる. 例えばガードインターバ ル先頭から FFT ウインドウを設定した場合には サブキャリア間の位相差はπ/2となるが、ガ ードインターバルとデータ部の境目から FFT ウ インドウを設定した場合には位相差は0となる. 同期処理部の FFT ウインドウ設定方法に依存し て、サブキャリア間の位相差が異なることにな るため、ベクトル平均によるフィルタリングで は図7に示すように平均化後の振幅値が本来の 値よりも小さくなる可能性がある.

図7 ベクトル平均による伝送路応答推定の問題点

ノイズ耐性向上手法 ロングプリアンブル部から計算された 52 本のサブキャリアに対する伝送路応答推定値を ref[i] (i=-26,-25,・・・26)とし、提案方式によるフィルタリング処理後の推定値

を REF[i]とする. 連続する 3 サブキャリア分の 伝送路応答推定値を用いて周波数軸方向にフィ ルタリングをかけ, 真中に当たるサブキャリア の補正を行う.

#### (1) 補正するベクトルの振幅値を計算

REF[- 26] = ref[- 26] |REF[j|| =  $\alpha \cdot |REF[j-1]| + \beta \cdot |ref[j]| + <math>\alpha \cdot |ref[j+1]|$ (i = -25, -24, ..., 25) (1)

ここで $\alpha$ ,  $\beta$ はフィルタリングの係数で、以下の関係を満たす.

$$2\alpha + \beta = 1 \tag{2}$$

(2) 補正するベクトルの位相値を計算 arg(REF[i]) =

$$\arg\left(\alpha \cdot \frac{\operatorname{REF}\left[i-1\right]}{\left|\operatorname{REF}\left[i-1\right]\right|} + \beta \cdot \frac{\operatorname{ref}\left[i\right]}{\left|\operatorname{ref}\left[i\right]\right|} + \alpha \cdot \frac{\operatorname{ref}\left[i+1\right]}{\left|\operatorname{ref}\left[i+1\right]\right|}\right) \qquad (3)$$

$$(i = -25, -24, ..., 25)$$

#### (3) 伝送路応答推定値の策定

式 (1) の振幅と式(3)の位相から求めたベクトルを REF[i]とする.

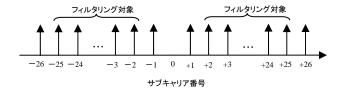

以上の操作を 52 本のサブキャリアに対して 行う (帯域両端, DC 両脇のサブキャリアの補正 はできないので実質的には図 8 に示すように 48 本のサブキャリアを補正する).

図8 IEEE802.11a のロングプリアンブルに対 するフィルタリング処理

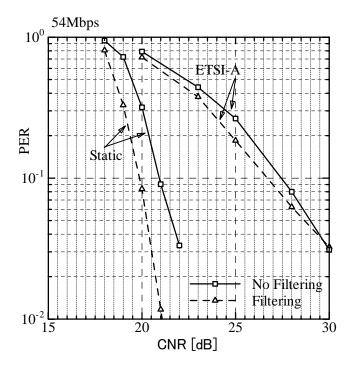

シミュレーション結果と考察 本方式による特性を評価するために、表 1 に示す条件により計算機シミュレーションを実施した。図 9 は提案方式(図中 Filtering と記載)と提案方式を用いない場合(同 No Filtering)におけるパケット誤り率 PER 特性を示す。提案方式を用いることにより、周波数軸方向のフィルタリングを行わない場合よりも PER=10%地点において Static 通信路で約 1 dB,ETSI-A 通信路[12]で約 0.8 dBの特性改善ができている。本提案方式で伝送路応答推定値にフィルタリングすることで雑音が抑圧され、より正確な復調処理が行われたことが判る。

表 1 IEEE802.11a 受信機の伝送路応答推定ノイズ耐性向上方式シミュレーション条件

| イス間は同工の以びてユレーンコンネト                                     |                                       |  |  |

|--------------------------------------------------------|---------------------------------------|--|--|

| Channel Model                                          | Static/ETSI-A<br>multi-path model[12] |  |  |

| AFC                                                    | あり[2]                                 |  |  |

| シンボル毎の位相<br>補正                                         | あり[2]                                 |  |  |

| Data rate                                              | 54Mbps<br>(64QAM,符号化率 3/4)            |  |  |

| Channel estimation filter tap coeff. $[\alpha, \beta]$ | [0.25,0.5]                            |  |  |

図9 IEEE802.11a 受信機伝送路推定部におけるノイズ耐性能力向上手法によるパケット誤り率

# W-CDMA モデムの構成と課題 3.1 3GPP DS-FDD システム[13]

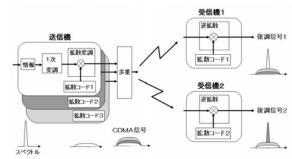

W-CDMA方式(3GPP DS-FDDシステム)は3GPP で規定された、DS-CDMA (Direct Sequence-CDMA)を無線アクセス方式として採用したシステムであり、一次変調にQPSK、二次変調にCDMAを用いる.ここで、DS-CDMAにおける多重分離の模式図を図10に示す。各ユーザ(コードチャネル)は、ユーザの情報レートより高速なレート(チップレート)で固有に割り当てられる拡散コードを使用することで、同一の周波数を使用する他ユーザとの分離が可能となる.

図10 CDMA における多重分離の模式図

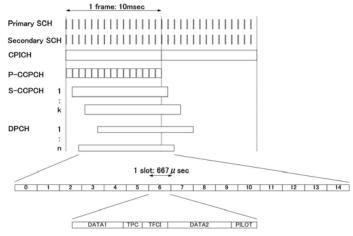

図11 W-CDMA システム物理チャネル構成

W-CDMAシステムでは3.84MHzのチップレートで情報の拡散を行い、基地局の送信(下り回線)には、基地局、セル固有に割り当てられた長周期の拡散コード(スクランブリングコード)と、チャネル毎に動的に割り当てられる短周期の拡散コード(チャネライゼーションコード)の2種類を重畳して使用する.移動端末の送信(上り回線)には、端末固有の長周期の拡散コードと、チャネル識別用の短周期の拡散コードの乗算されたものが基本コードとして使用される.

図11にW-CDMAシステムの下り回線チャネル構成を示す[14].下り回線チャネルは、共通チャネルと個別チャネルに大別され、さらに共通チャネルには報知情報を送信するチャネル(P-CCPCH)、複数のユーザで共用するチャネル(S-CCPCH)、および端末受信機で信号の復調に使用されるパイロットチャネル(CPICH)がある。また、移動端末が基地局識別を行う手順に使用される2種類の同期チャネル(Primary SCH, Secondary SCH) もある.一方、個別チャネル(DPCH)はユーザ個別に割り当てられたチャネルで、音声や画像などの情報の伝送に使用される.

端末の移動に伴う受信レベルの変動 (フェージング変動) により受信データ列に誤りが生ずる場合があるが,このようなビット誤りに対する訂正技術として,音声などの比較的低速な情報レートのデータには畳み込み符号化,パケッ

トなど比較的高速な情報レートのデータにはターボ符号化が使用される. また, 無線環境では誤りはバースト的に発生するという特徴があり, データ列の送信順序を入れ替えるインターリーブ技術を併用することでバースト誤りを散発的な誤りに変換した上で訂正を行うことができる.

なお、CDMA方式では同一の周波数を出来るだけ多くの複数ユーザで使用するため、1 ユーザ当りの送信電力を極力小さくする必要がある.この課題を解決するために、W-CDMAシステムでは下り/上り回線とも、受信品質に基づいて送信電力を制御する送信電力制御が適用されていうとして基地局に対して制御情報を送ることで実現し、上り回線の電力制御は基地局が受信品質を測定して移動機に制御情報を送ることで実現して移動機に制御情報を送ることで実現して移動機に制御情報を送ることで約667  $\mu$  sの制御周期ごとに1dB単位で送信電力を制御することで、高速なフェージング変動の場合でも最適な送信電力を維持することができる.

#### 3.2 W-CDMA 受信信号処理と受信機構成

CDMAでは、高速なレートの拡散コードを用いることで図1の様な異なる方向から到来した反射波を分離できる特徴を持っており、分離した

複数の反射波を合成することで受信品質を向上させることができる.これを実現するための受信機はRAKE受信機と呼ばれており,図12に示すように、マルチパス毎の素波受信機(フィイガ)からの出力を同相合成することでパスダルーシチ効果を得ることができる.また基地局からの信号も分離することができ,パスニとができるができるが、RAKE受信機で合成ダイバーシチと同様、RAKE受信機で合成ダイバーシチと同様、RAKE受信機で合成ダイバで更なるダイバーシチカ果(マクロダイバでよび、大変を機能を用いてソフトハンドオーバを実現し、セル周辺での通信品質を向上する.

図12 RAKE受信機における信号処理

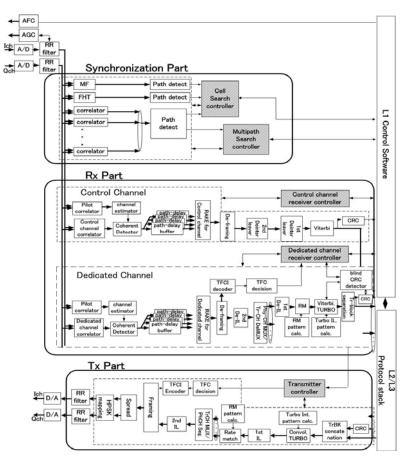

図13 W-CDMAモデム部機能ブロック図

以上の様に端末受信機ではRAKE受信機を使用した通信を行うが、通信開始に先立ち同期チャネル等を利用して受信可能な基地局のサーチを行う必要がある。また受信可能な基地局はユーザの移動に伴い遷移するため、通信中にもパイロットチャネル等の受信レベル観測や共通制御チャネルの受信を行う必要がある。これら一連の処理を実現するためのW-CDMA端末機能ブロック構成例を図13に示す。

2.2で示した無線LANモデムと同様,受信系処理は大きく同期部と受信処理部に分割され,同期部では同期チャネルの検出,拡散コード同期を行い,この情報を基にして受信処理部での処理を行う.

受信処理部では RAKE 合成を行った後,フレームフォーマットに則って信号を集めて 2nd デインターリーブを行い、トランスポートチャネル分離を行った後で 1st デインターリーブを行う。更に、レートマッチングブロックでフォーマットにより規定されたビット数に合わせるように復調ビットの追加/合成を行い、チャネルコーデックの種類に応じてビタビデコード/ターボデコードを行う。最後にブロック毎の CRC を求め、2層プロトコルへデータ転送を行う。

#### 3.3 W-CDMA 受信機における課題

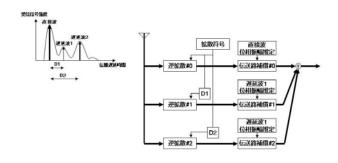

CDMA システムでは、拡散を行わないディジタル変調システムに比べ、コード同期捕捉、追随に関する技術が必要となる。本稿では、マルチパス環境に応じて RAKE 受信機のフィンガタイミングを制御するためのパスサーチアルゴリズムに関する一手法を紹介する[15]、[16]。簡単な構成の RAKE 受信機では、専用の相関器(パスサーチャ)を使用してパスサーチを行い、検出したパスタイミングを直ちにフィンガへ割り当てる方法が検討されているが[17]、本方式はパスサーチャと RAKE 相関器の両方からの情報を利用してフィンガ割り当て判定を行う。

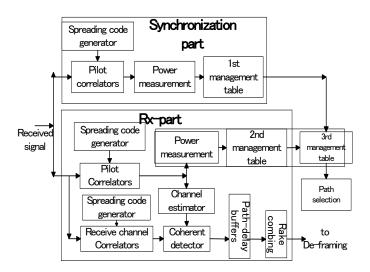

提案方式 図14に示すように提案するアルゴリズムでは、パスサーチャからの情報を保持するためのテーブル1と RAKE 合成用の相関器からの情報を保持するためのテーブル2を使用し、さらにこれら2テーブルの内容を合成したテーブル3から高順位ものを次の RAKE 合成すべきパスと決定する. ここで、相関値の計算は受信信号に多重されているパイロットチャネルを用いる.

#### (テーブル1の更新方法)

(1) 窓幅内の相関電力値上位 10 パスを選択する. (2) 過程 1 で得られた相関電力値に係数  $(1-\alpha)$  を掛け合わせる.  $(0=<\alpha<1)$

(3)テーブル1上の相関電力値に係数 $\alpha$ を掛ける. (4)過程2と3で同じ遅延時間であるパス同士の相関電力値を加算してテーブル1を更新する.

#### (テーブル2の更新方法)

(1) RAKE 相関器に割当られたパスの相関電力値を計算し係数 $(1-\beta)$ を掛ける.  $(0=<\beta<1)$  (2) テーブル 2 上の相関電力値に係数  $\beta$  を掛ける. (3) 同じ遅延時間であるパスの相関電力値を加算してテーブル 2 を更新する.

#### (テーブル3の作成)

- (1) 同じ遅延時間のパスに対してテーブル 2 の値を $\gamma$  (>1) 倍した値とテーブル 1 の要素を加算する.

- (2)テーブル3要素を相関電力値の大きい順番に並べXdB以上のパスをRAKEフィンガに割当てる.

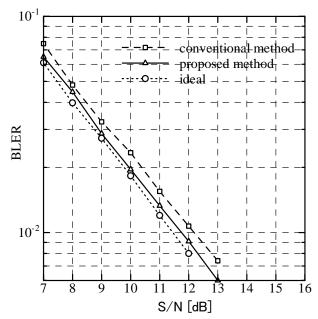

シミュレーション結果 本提案方式を使用した場合のシミュレーション結果 (ブロック誤り率 BLER) を図 15 に示す.尚,比較のためにパスサーチが理想的に行われた場合の結果 (ideal) とパスサーチャ (テーブル1) のみを使用した場合の結果も示す.RAKE 相関器情報を利用した本提案方式では、パスサーチャの結果を即時に使用するアルゴリズムよりも BLER=1%地点において約0.4dB 特性が向上している.これは RAKE 相関器からの情報を使用することで前の時点に捕捉していたパスの電波に加重がなされ、雑音環境で強度の高いパスを見失う確率を下げる働きが生じるためである.

図14 RAKE 受信機におけるパス管理テーブルを用いた伝送路応答推定能力向上の一手法

表2 W-CDMA 受信機における伝送路応答推定 能力向上方式シミュレーション条件

| 配が同土が対すてユア                      | マコマ木口                                                         |

|---------------------------------|---------------------------------------------------------------|

| Spreading factor                | 128                                                           |

| Data rate<br>(Data channel)     | 12.2 [kbps]                                                   |

| Chip rate                       | 3.84 [Mcps]                                                   |

| Demodulation                    | Pilot symbol assisted coherent detection                      |

| Channel coding                  | Convolutional coding<br>(R=1/3, K=7)<br>Soft-decision Viterbi |

| Interleaving                    | 20 [m sec]                                                    |

| Rake fingers                    | 4                                                             |

| Path search period              | 100 [m sec]                                                   |

| Assign threshold T <sub>1</sub> | 17 [dB]                                                       |

図15 W-CDMA 受信機における伝送路応答推 定能力向上方式シミュレーション結果

#### 4. W-CDMA に向けたモデム構成の検討

W-CDMA端末を実現するためには、ベースバンド信号処理・制御を行うベースバンドLSIが重要な開発要素としてあげられ、送受信性能以外に以下のことが要求される[18]-[20].

(1) 低消費電力: W-CDMA方式は,従来に比べ 非常に多くの信号処理,高速制御が必要である が,携帯電話として使用できる電池は大きさ/ 容量/重量に制限されるため,LSIの低消費電力 化が必須である.その実現には最適な信号処理 アルゴリズム開発とそれを実現する回路規模削 減、さらに低消費電力微細化プロセスを使用することがもっとも重要なファクタとなる.

- (2) 低リーク電流:LSI内部のレジスタやメモリなど電源を切ることのできない回路がある. 待受け時間の長時間化にはこのような回路に流れる電流(リーク電流)がきわめて低いことが必要である.

- (3) ローコスト/小型化/高集積化:携帯電話としては、小型および低価格であることが常に要求される.このためにはLSI化によるメリットを十分に活かすため、微細化プロセスを使用するだけでなく最適な機能分割をしたチップセット構成が必要である.この機能分割は、アナログ/ディジタル回路、信号処理のハード化/ソフト化のパーティショニングなどシステム的に多方面から検討を行う.

#### 4.1 信号処理量見積もり

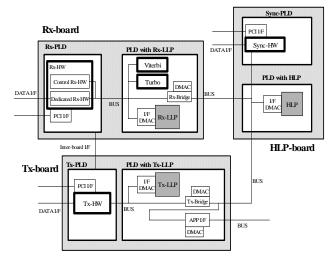

評価対象システムである W-CDMA 端末の処理量を測定するために、ソフトウエアシミュレータを開発し CPU エミュレータを用いて端末部 MIPS 見積もりを行った。同システムの端末では、図13に示した様に CDMA 信号の初期同期捕捉、マルチパス追随を行う同期部 (Synchronization Part)、制御チャネル (Control Channel) と専用通信チャネル (Dedicated Channel) を独立に RAKE 受信する受信部 (Rx Part) 、送信データを生成し拡散変調する送信部 (Tx Part) からなり、これら物理層の機能が通信プロトコルや制御ソフトによってコントロールされる.

なお、3GPPでは複数のサービスがサポートされており[13]、それぞれ要求される処理量が異なる、端末側の通信の形態を考えると、ウエブブラウジングやファイルダウンロードなど、一般的に下り回線の通信速度が要求される。ここでは、下り回線 384kbps パケット+12. 2kbps データ+3. 4kbps データの処理を仮定し、端末内で行われる信号処理量を見積もる. なお、端末モデルプログラムは LSI実装を想定して、32Bit 幅固定小数点演算で記述した。それぞれの処理量評価の結果を表3、4に示す。

表3 端末同期系における処理量の評価

| Function    | MIPS   |

|-------------|--------|

| MF          | 7551.5 |

| FHT         | 15.3   |

| Correlator  | 2961.4 |

| Path detect | 26.2   |

表 4 端末受信系における処理量の評価

| Function                                                 | MIPS    |

|----------------------------------------------------------|---------|

| Correlator                                               | 13334.4 |

| Channel estimate,<br>Coherent detect, RAKE               | 1504.0  |

| Channel decoder<br>(Viterbi + Turbo)                     | 3732.0  |

| 1st deinterleaver (De-IL)                                | 11.0    |

| Rate matching (incl. Parameter calc.)                    | 19.7    |

| 2 <sup>nd</sup> De-IL                                    | 9.2     |

| CRC Check                                                | 4.9     |

| TFCI decoder                                             | 5.8     |

| Others                                                   | 32.2    |

| (De-framing, TRCH DeMUX, Turbo<br>IL pattern calc., etc) |         |

#### 4.2 モデム構成と回路規模

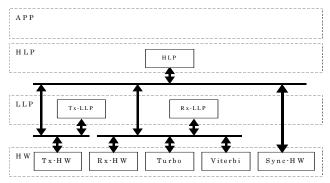

商用に向けたモデム LSI を実現するためには, サイズ、消費電力、コストの問題を常に意識した 設計が必要となる. これらの課題に対して, 先端 の無線システムに向けた端末では、ハードウエア による実装が重要となるが、一方で無線機に必要 とされる柔軟性とのトレードオフを考える必要 がある. このため、モデム LSI では、柔軟性に考 慮したハード/ソフトの分割とそれに併せたア ーキテクチャの検討が必要である. 次に, ソフト ウエア比率の大きいモデムでは、効率的なソフト ウエア処理の実現が重要である. 本来, ソフトウ エア処理は冗長が多いため, ソフトウエア自体の 効率化がモデム全体の効率化につながることに なる. そのためには, OS の利用の要否や, 処理内 容に応じたプロセッサの選択を考える必要があ る.後者に関し,算術演算的な複雑性に対しては DSP 利用による処理効率の向上なども考えられる. 4. で示したベースバンド LSI における課題に対 し、本章では信号処理の性質により機能分割を行 う階層化アーキテクチャと、これを効率的に実現 するバス構成を提案する.

#### (階層化アーキテクチャ)

モデムアーキテクチャは、内部で使用する組み込みプロセッサの処理能力に大きく影響される。特にソフトウエア処理の多いソフトウエア指向モデムでは、その傾向が顕著に現れる。現在、携帯端末用に使用される組み込みプロセッサの動作周波数は高々数百 MHz であり、無線信号処理をソフトウエアで実現するためには複数のプロセッサを使用する必要がある[20]-[24]。さらに、3G システムの様に端末側の信号処理に負荷がか

かるシステムの場合には、部分的にハードウエア を使用することで消費電力やLSI 実装サイズを削 減できる.

ところで、一般にモデム内の物理層に近い信号処理は無線インターフェースの時間制約を受け、また、算術演算が多用される。一方、上位層に近い処理は、無線インターフェースの時間的拘束はゆるく、制御に伴う条件分岐等の処理が多い。この様に、上位層、下位層の処理でプロセッサに要求される能力が異なるため、処理に適したプロセッサ種別や RTOS 採用を含めて考えると、処理階層毎にプロセッサを分割したアーキテクチャが有効と予想される。この様な理由から、本稿では処理内容にあわせてプロセッサ処理を分割する、階層化アーキテクチャを紹介する[18]-[20].

図16は、本提案の概念を示したものである. 端末内で行う処理をここでは以下の4つにカテゴリ分けし、その内容に応じてプロセッサの使用を考える.

- (1) 処理速度要求が非常に高い処理,または, ビット幅が小さく(大きく)プロセッサで 行うには効率の悪い処理.

- (2) 無線フレームに起因する割込み応答時間 など,時間的拘束が強い処理.

- (3) 複数処理の同時実行や、制御などの条件分岐の多い処理.

- (4) 端末のH/Iやアプリケーションの様に信号 処理の影響を極力排除したい処理や,通信 プロトコル下位層へのインターフェース.

(1)は動作クロックがCPUクロックを超える様な 処理や、ビット幅が1ビットの処理(逆に極端に ビット幅を要求する処理)に相当する. これらは プロセッサで実行するには負荷が重く,消費電力 や規模の面からハードウエアの適用が望ましい (図16-HW層). また, (2)の処理はハードウエ アからの割り込みが多い制御や、ある程度まとま った量の信号処理をこなすプロセッサ処理が可 能である(図16-LLP層). (3)の処理は,要求応 答速度が長い処理や複雑な演算, あるいは通信プ ロトコル処理の一部や物理リソースの制御など, 信号処理と制御の入り混じった処理となる.この ため、この処理を実行するプロセッサは複数のタ スクを同時実行することになり, RTOS 採用による ソフト開発効率の向上も考慮する必要がある(図 16-HLP層). (4)は上位通信プロトコル処理, ア プリケーション処理などを行うプロセッサで,メ モリ空間やマルチメディア関連能力を要求され る処理を担当する (図16-APP 層). この様に, プロセッサを複数に分割して, なおかつ, 各階層 間の情報伝送頻度を考慮することで、割込み処理 によるオーバヘッドを低減することが可能とな る.

図16 3G システム向けモデム内のハード /ソフトの切り分けとバスアーキテクチャ

各階層の処理分担は、大枠では上述の通りであるが、各層間のデータ転送を削減し負荷を軽減する工夫や、共通の処理に対するリソースの共用化などを行うことで効率化を図ることができる.

ここでは 4.1 で行った処理量見積りを基に,要求 MIPS 数とプロセッサの処理能力,ブロック間 データ転送の効率,機能の柔軟性の 3 点に注意してモデムの機能分割を行った.

#### (1)要求 MIPS 数とプロセッサ処理能力

低消費電力で組み込み向けに使用可能なプロセッサの動作周波数は数 100 MHz 程度であり、これに比べ負荷の大きい信号処理はハードウエアへ機能割り当てを行う。表 4 の受信系処理量見積もりの結果から、RAKE 受信処理(図 1 3 : Correlator、Channel estimator、Coherent detector、RAKE)、チャネルコーデック復号処理(Channel decorder)はハードウエア実装とする。また送信系拡散処理(Spread)は 1 bit 演算が多用され、しかも高クロックでありハードウエア実装は消費電力的に有利である。また、表 3 から同期系のマッチドフィルタ(MF)、相関処理(FHT、correlator)も同様にハードウエア割当てを行う。

#### (2)データ転送の効率化

効率面から、機能ブロック間のデータ転送を抑えた割り当てを行うことで、消費電力的な考慮を行う、まず、送信/受信処理は、処理シーケンスの連続性や処理内容の違いから、異なる LLP に分割した。また、FHT や CRC 処理の様に、処理量の小さい機能でもデータ転送の効率からハードウエア実装を行う。同期系に関しては、待ち受け時の消費電力を極力削減するために、送受信号処理を受け持つプロセッサ(Rx-LLP, Tx-LLP)から独立したほうが良い。このため、同期系ハードウエアは HLP から直接制御する形を取り、図16に示す様な機能分割を行った。

#### (3)柔軟性

3GPP 規格から、フレーミング、トランスポートチャネルの分離/合成、インターリーブ、レートマッチングの処理はチャネル組合せに自由度を必要とする機能である.これらは、サポートチャネル選択に対する柔軟性やソフト変更によるサポートチャネル切替の点から、ソフトウエア実装が適している.(1)、(2)のハードウエア割当ての結果、Rx-LLPには72.1MIPS程度の処理量でインターリーバ、レートマッチング処理、フレーム結合と制御プロセスを割当てることが可能となる.

図17はこの機能分割を階層化アーキテクチャに則り実装した評価ボードの模式図である. なお,図17における各信号の流れは,図16のツリー状バスにより実現している.以上のような機能分割を行うことで,消費電力や回路規模を抑えつつ,ユーザの要求に応じてソフトウエアの変更を行うことで新たなサポートサービスを提供可能なモデムを実現できる.

図17 評価ボードに対する提案アーキテクチャの実装形態(Tx-HW は未実装)

表5 ハードウエア部のゲート数とメモリ量

|                                | <b>Logic</b><br>(kGate) | Memory<br>(kbit) |

|--------------------------------|-------------------------|------------------|

| Rx-HW                          | 354                     | 145              |

| Sync-HW                        | 72                      | 72               |

| Turbo Decoder<br>(incl. CRC)   | 61                      | 190              |

| Viterbi Decoder<br>(incl. CRC) | 30                      | 28               |

| Bridge                         | 34                      | 0                |

|                                | 551                     | 435              |

表6 各プロセッサのメモリ使用量

|        | IMEM<br>(kB) | DMEM<br>(kB) |

|--------|--------------|--------------|

| HLP    | 135          | 113          |

| Rx-LLP | 48           | 127          |

| Tx-LLP | 48           | 113          |

|        | 231          | 353          |

#### 5. むすび

本稿では移動通信用復調信号処理の基礎とし て,無線 LAN システム,3G セルラーシステム受 信機の信号処理を解説し,また3Gセルラーシス テムについてはモデム LSI 設計に関連する処理 量見積もりやモデム LSI におけるソフト/ハー ドの機能分割方法について述べた. 無線 LAN シ ステム, 3G セルラーシステムについては更に詳 細な文献が出ており、一歩踏み込んだ知識が必 要な方はこれらの文献を一読されることをお勧 めする[25]-[27].

#### 参考文献

- [1] IEEE 802.11a, 1999 Edition,

- http://standards.ieee.org/getieee802/802.1

- [2] Akita, K.; Sakata, R.; Sato, K.; "A phase compensation scheme using feedback control for IEEE802.11a receiver" IEEE VTC2004-Fall. Volume 7, pp. 4789 - 4793 Sept. 2004

- [3]P. H. Moose, "A technique for orthogonal frequency division multiplexing frequency offset correction," IEEE Trans. Commun., Vol. 42, No. 10, pp. 2908-2914, Oct. 1994

- [4] M. Speth, S. A. Fechtel, G. Fock, and H. Meyr, "Optimum receiver design for wireless broad-band systems using OFDM-Part I," IEEE Trans. Commun., Vol. 47, No. 11, pp. 1668-1677, Nov. 1999

- [5]佐方連, 佐藤一美. "IEEE802.11a 通信におけ るマルチパス耐性のある時間同期方式の検討 "信学ソ大, B-5-168, 2003

- [6]原田慎也, 佐方連, 佐藤一美, "IEEE802. 11a 通 信におけるマルチパス伝搬路に耐性のある時間 同期方式の検討"信学総大, B-5-227, 2004 [7]旦代智哉, 佐藤一美, 行方稔, "IEEE802.11a 時間同期方式の検討"信学総大, B-5-253, 2002 [8] 佐方連, 秋田耕司, 佐藤一美, "IEEE802.11a 受

- 信機における高速位相追従方式"信学技報, RCS2004-62 pp. 37-42 May 2004

- [9]三ツ木淳,瀬戸一郎,向井学,"OFDM受信機に おけるDCオフセット補償に関する一検討",信学 ソ大, B-5-189, 2005

- [10]秋田耕司, 佐藤一美, "IEEE802.11a 受信機

- における位相補正方式の一検討"信学ソ大, B-5-169, 2003

- [11] 三ツ木淳,佐藤一美," IEEE802.11aにおけ る伝送路応答推定方式に関する検討",信学総大, B-5-228, 2004

- [12]ETSI/BRAN document no. 3ERI085B, 1998

- [13]3GPPSpecifications, http://www.3gpp.org

- [14] 3GPP TS25. 211 v3. 5. 0

- [15]三ツ木淳,向井学,鶴見博史,"CDMA システムにおけるパスサーチ方式の検討",信学総大, B-5-188, 2002

- [16] J. Mitsugi, M. Mukai, H. Tsurumi, "Path Search Algorithm Introducing Path Management Tables for a DS-CDMA Mobile Terminal", pp. 730-734, PIMRC2002, 2002

- [17] S. Fukumoto, K Okawa, K. Higuchi, M. Sawahashi and F. Adachi "Path Search Performance and its Parameter Optimization of Pilot Symbol- Assisted Coherent RAKE Receiver for W- CDMA Mobile Radio", IEICE Trans. Fundamentals, Vol. E83-A, No. 11 pp. 2110-2119, November 2000.

- [18]M. Mukai, et al., "A Software Oriented Modem Architecture for 3G Terminal",

- VTC2003 fall, Oct. 2003 [19]向井学,他,"階層化アーキテクチャによる ソフトウエア無線機用モデム",信学論文誌 B, Vol. J88-B No. 4, p. 728, April 2005

- [20]向井学,他, "UMTS に対応したソフトウエア指向モデムアーキテクチャの提案と試作",ソフトウエア無線研究会,SR03-3,2003

- [21]上原一浩,鈴木康夫,芝宏礼,田中裕之,浅井祐介,庄納崇,久保田周治"マルチプロセッサ・アーキテクチャを用いたソフトウエア無線機における全二重リアルタイム通信を実現するためのソフトウエアの設計と評価",信学論文誌 B, Vol. 184-P No.7 1909 July 2001 J84-B No. 7, p. 1208, July 2001

- [22]H. Harada and M. Fujise, "A New Small-Size Multi-Mode and Multi-Task Software Radio Prototype for Future Intelligent Transport Systems", IEICE Trans. Comm., Vol. E85-B, No. 12, p. 2703, Dec. 2002 [23]矢野隆,前田裕之,石井裕丈,鈴木芽衣,加藤猛, 土居信数,"W-CDMA 端末用ベースバンドモデム LSI の評価",信学ソサイエティ大会,B-5-134,

- [24]富澤武司,向井学,鶴見博史,"UMTS に対応したソフトウエア指向モデムの試作ボードにおける評価",ソフトウエア無線研究会,SR03-22, 2003

- [25]守倉正博, 久保田周治, "802.11 高速無線

- LAN 教科書",インプレス社発行 [26]立川敬二,"W-CDMA 移動通信方式",丸善株 式会社発行

- [27] 横山光雄, "スペクトル拡散通信システム", 科学技術出版社発行