## 次世代 CMOS(Ge/III-V チャネルとトンネル FET) の研究開発の現状

## Present status of research and development of next generation CMOS (Ge/III-V channel and tunnel FET)

宮本 恭幸<sup>†</sup> Yasuyuki MIYAMOTO<sup>†</sup>

†東京工業大学電子物理工学専攻 Dept. Physical Electron., Tokyo Tech.

## 概要

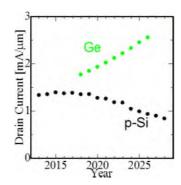

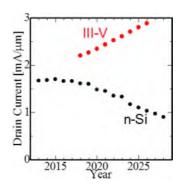

最近の集積回路の性能向上は微細化だけでは望めず、テクノロジーブースターと呼ばれる新しい技術をいれないと進歩が望めなくなってきた。特にシリコンだけでは、今後微細化に伴いドレイン電流が減るという今までにない傾向が予測され、その打破の為に高移動度チャネルをテクノロジーブースターとして導入することへの期待が高まっている。本報告では、p-MOSFET の為の高移動度チャネルとして期待される Ge チャネル、n-MOSFET の為の高移動度チャネルとして期待される III-V チャネルの現在の開発状況を説明した後、低消費電力用回路の為のテクノロジーブースターとして期待されるトンネル FET を紹介する。

図1 p-MOSFET のオン電流の将来予測

図 2 n-MOSFET のオン電流の将来予測

## **Abstract**

Recent progress of the integrated circuit cannot be obtained simple scaling and introduction of "technology booster" becomes essential. At present, decrease of drain current by Si channel is expected in the future. To defeat this tendency, introduction of high mobility channel is expected. In this report, present status of research and development of Ge channel for p-MOSFET and III-V channel for n-MOSFET is explained. As new technology booster for low power consumption, tunnel FET is also explained.