# MMIC 設計の基礎

# Fundamentals of MMIC Design Technology

小野 直子

#### Naoko Ono

(株) 東芝 研究開発センター

Corporate Research & Development Center, Toshiba Corporation 1, Komukai Toshiba-cho, Saiwai-ku, Kawasaki 212-8582, JAPAN Tel:+81-44-549-2280, Fax:+81-44-520-180, E-mail: nao.ono@toshiba.co.jp

#### **Abstract**

MMIC technology is important because it enables high-frequency equipments and components to reduce the size. This session presents an overview of fundamental MMIC technology, including its structures and elements. Also, circuits and design methodologies will be described during the session.

#### 1. はじめに

モノリシックマイクロ波集積回路(MMIC:monolithic microwave integrated circuit)とは、一つ以上の高周波回路ブロックの全てを、一つの半導体基板上に設ける高周波集積回路である。MMICは、能動素子および受動素子を半導体製造プロセスによって一括で一体形成することができる。半導体基板材料には、ヒ化ガリウム(GaAs)、シリコン(Si)等が用いられる。能動素子とは、トランジスタ、ダイオード等である。受動素子とは、伝送線路、インダクタ、キャパシタ、抵抗、加えて受動機能素子等である。

マイクロ波帯、ミリ波帯の高周波装置・部品を小型化するためには、高周波回路の MMIC 化技術が重要である。本講義では、MMIC ならではの構造、素子、回路例、設計手法を解りやすく解説する。

## 2. 高周波回路部品の歴史

半導体微細加工技術の飛躍的な発展に伴い、 トランジスタの高周波化、半導体チップ上の回 路の集積化が進んでいる。一つの半導体チップ 内に形成される回路は、従来の単体能動素子か ら、機器の一つの回路機能を果たす回路ブロックへ、更には、複数の回路ブロックへと集積化度が高くなってきている。これに伴いマイクロ波集積回路(MIC: microwave integrated circuit)の実現形態は、ハイブリッド集積回路(HIC: hybrid integrated circuit)またはハイブリッドマイクロ波集積回路(HMIC: hybrid microwave integrated circuit)化、MMIC化が進んでいる。

HICとは、一つの回路ブロックを、トランジスタ等が形成された半導体チップと、チップの周辺に外付けで実装される受動部品とを組み合わせて実現する回路形態のことである。

MMICとは、前述の通り、一つの回路ブロックを一つの半導体チップ内に全て形成する回路形態である。HICと比べ、高周波回路部品の小形軽量化が図れ、実装コストを低減できるため、注目を集めている技術である。

## 3. MMIC の構成

MMICは、半導体製造プロセスにより、半導体基板上に能動素子および受動素子を一括形成するものである。能動素子は半導体基板表面近傍に形成される。これに対し、受動素子、とり

| 種類                      | 伝送線路部の構造的特徴        | 伝送線路部の工程的特徴       |  |

|-------------------------|--------------------|-------------------|--|

| マイクロストリップ線路型MMIC        |                    | 半導体基板部のヴィアホール工程あり |  |

|                         | 半導体基板部にヴィアホールあり    | 裏面研磨工程あり          |  |

| コプレーナ線路型MMIC            | 半導体基板の主面にメタル層あり    | エアーブリッジの工程あり      |  |

| コフレー )<br>R M 全 M M I C | 半導体基板の主面にエアーブリッジあり | エアーフリックの工程のの      |  |

| 薄膜誘電体層付きMMIC,           | 半導体基板の主面にメタル層あり    | 薄膜誘電体層形成工程あり      |  |

| 3次元MMIC                 | 半導体基板上に薄膜誘電体層あり    | 将族的电体信心以上性の9      |  |

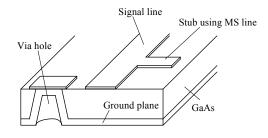

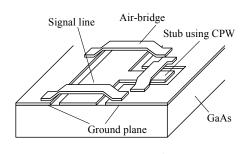

(a) マイクロストリップ線路型

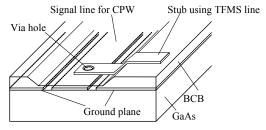

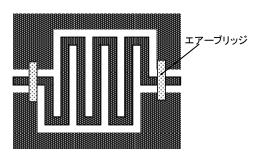

(b) コプレーナ線路型

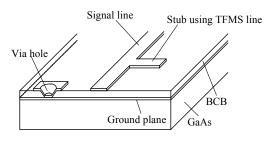

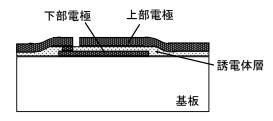

(c) 薄膜誘電体層付 MMIC と 薄膜マイクロストリップ線路

図1 MMIC 伝送線路部の構造

わけ伝送線路は、線路種類毎に形成される部位が大きく異なるため、MMIC 構成も線路種類に依存して、配線メタル層、誘電体層の構造が異なる。

MMIC 構成の種類を表1に示す。MMIC の一

般的な構成は、マイクロストリップ線路型 MMIC、コプレーナ線路型 MMIC、薄膜誘電体 層付3次元MMICの3種類に大別される。MMIC 伝送線路部の構造を図1に示す。

図1(a)のマイクロストリップ線路型 MMIC

は、半導体基板の素子形成面である主面と裏面 にメタル層を設け、両メタル層を接続するため 半導体基板にヴィアホールを設ける構成である。 伝送線路としてマイクロストリップ線路 (MSL: microstrip line) を用いる MMIC である。 線路の構成は、誘電体層として半導体基板を用 い、基板の主面に信号線用メタルパターンが、 裏面にグラウンド用メタルパターンがそれぞれ 形成される。つまり、線路の特性インピーダン ス (Z0) を  $50\Omega$  等所望の値にするために、研磨 加工により基板の厚みを制御する必要がある。 基板の厚みは、50~200μm程度である。加えて、 半導体基板の主面と裏面のグラウンドを接続す るために基板のヴィアホール加工が必要である。 更に、半導体基板が薄いためハンドリングが困 難である等課題が多い。

図1(b)のコプレーナ線路型 MMICは、半導体基板の主面にメタル層を設け、加えて、メタル層上に必要に応じてエアーブリッジを配置する構成である。伝送線路としてコプレーナ線路(CPW: coplanar waveguide)を用いる MMICである。線路の構成は、信号線用メタルパターン、グラウンド用メタルパターンとも半導体基板の主面に形成される。つまり、半導体基板の研磨加工、裏面メタル形成、ヴィアホール加工が不要な、マイクロストリップ線路型 MMICより安価な構造である。但し、コプレーナ線路の

信号線両側のグラウンド用メタルパターンを同 電位に保つためエアーブリッジ形成工程が必要 である。

図1(c)の薄膜誘電体層付 MMIC は、半導体基板の主面に、一層以上の誘電体薄膜層と、メタル層を交互に積層する構造である。伝送線路の誘電体として薄膜誘電体層を用いる。伝送線路として、薄膜マイクロストリップ線路(TFMSL: thin-film microstrip line)、薄膜逆マイクロストリップ線路等を用いることができる。これらの線路は、コプレーナ線路と同様に、半導体基板の研磨加工等が不要である安価な構造である。

薄膜誘電体層材料には、ポリイミド、BCB (benzo-cyclo-butene)等が用いられる。誘電体層の厚みは数 μm 程度である。なお、シリコン系半導体のディジタル LSI プロセスを用いる場合には、薄膜誘電体層としてシリコン酸化膜が一般的に用いられる。誘電体層の厚みは数百 nm から 1μm 程度であり、メタル層数が数層程度と多い傾向にある。

### 4. MMIC に用いられる回路素子

## 4.1.能動素子

MMIC に使用される主な能動素子は、化合物 半 導 体 系 で は GaAs MESFET (metal-semiconductor field effect transistor)、 GaAs HEMT (high electron mobility transistor)、 GaAs PHEMT (pseudomorphic HEMT)、InP HEMT、GaAs HBT (heterojunction bipolar transistor)、Si系では、SiGe HBT、BiCMOS、バイポーラトランジスタ、MOSFET等である。

半導体材料の移動度とエネルギーギャップを表2に示す。半導体材料には、電子の移動度(Ue)およびホールの移動度(Uh)が存在する。一般的に移動度が大きいほど高周波に適している。また、エネルギーギャップが大きい程、高出力デバイス等に適している[1]。

表2 半導体材料の移動度と エネルギーギャップ

| 半導体種類 | 移動度Ue<br>(cm²/V-s) | 移動度Uh<br>(cm²/V-s) | Ue/Uh | エネルギーギャップ<br>(eV) |

|-------|--------------------|--------------------|-------|-------------------|

| Ge    | 3900               | 1900               | 2     | 0.7               |

| Si    | 1500               | 500                | 3     | 1.1               |

| GaAs  | 5000               | 400                | 12.5  | 1.43              |

| InP   | 4000               | 100                | 40    | 1.25              |

Ue: Electron mobility

Uh: Hole mobility

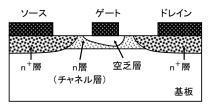

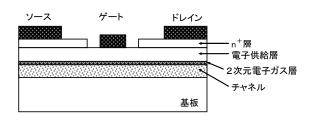

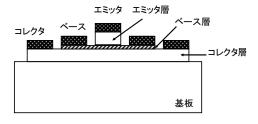

(a) GaAs MESFET

(b) GaAs HEMT

(c) バイポーラトランジスタ図2 能動素子の基本構造(断面図)

主な能動素子について以下に述べる。

GaAs MESFETの構造を図2 (a)に示す。

GaAsには、SiO<sub>2</sub>のような絶縁膜として用いる良質な酸化膜が存在しないため、MOSFET構造は困難である。半導体と金属の界面に形成されるショットキー障壁を利用したMESFET構造が用いられる。GaAs MESFETは、ゲートに印加する電圧を変化させることで、ゲート直下の空乏層の厚さを変化させることにより、ソースからドレインへ移動する電子の量を制御することで動作する。MESFETは低価格化に向くデバイスであるが、特性に影響を与えるしきい値のバラツキが大きい。

GaAs HEMT の構造を図 2 (b)に示す。HEMT は、キャリアを供給する電子供給層とキャリアが走行するチャネル層が分離された構造の FET である。 2 次元電子ガス層を電子走行層として用いる。ゲートは、ショットキー障壁を利用している。GaAs HEMT は、ゲートに印加する電圧によりヘテロ界面のポテンシャルを制御し、 2 次元電子ガス層の電子数を増減させることで動作する。なお、HEMT 構造において、チャネル層に GaAs より移動度が高い InGaAs を用いたものが GaAs PHEMT と InP HEMT である。HEMT は、ミリ波帯の特に低雑音デバイスとして有力である。

バイポーラトランジスタの構造を図2(c)に示す。高周波特性が優れるのは、電子の移動度が大きいnpn型であり、エミッタ層とコレクタ層がn層、ベース層がp層となる。HBTには、化合物半導体系とSi系がある。基本構造は図2(c)と同様である。HBTは、エミッタとベースがヘテロ接合されている。エミッタにベースよりバンドギャップの大きな半導体を用いることにより、電流利得を大きくとれるという特徴がある。HBTは、FETと異なり、エミッタ・コレクタ間を縦方向に電流が流れ、その電流量をベースで制御する。GaAs HBTは高利得、高効率を実現でき、パワーアンプに適している[2]。

## 4. 2. 伝送線路

MMIC に用いられる伝送線路について述べる。 図1(a)のマイクロストリップ線路は、簡単な構造の線路であり、従来から MMIC に最も広く使われてきた線路である。市販のマイクロ波回路シミュレータが持つマイクロストリップ線路のエレメントモデルが充実しているため、回路設計を比較的容易に行なうことができる。但し、半導体基板の材料とその厚みが固定されると、Z0に依存して信号用メタルパターンの幅が決まるという制約がある。

図1(b)のコプレーナ線路は、従来から

MMICに広く使われてきた線路である。線路の Z0 は、信号線用メタルパターン幅とギャップ幅 によって決まる。つまり、Z0 をメタル幅とギャップ幅の複数の組み合わせで実現できる。 しかし、信号線用メタルパターンの両側に幅の広いグラウンド用メタルパターンが必要であるため、MMIC の小型化に限界がある。 更に、レイアウト設計の自由度がマイクロストリップ線路に比べて小さい。加えて、市販の回路シミュレータが持つコプレーナ線路のエレメントモデルが不十分であるため、電磁界解析等によるモデル作成が必要な場合が多い。

図1(c)の薄膜マイクロストリップ線路は、 薄膜誘電体層付 MMIC へ形成する線路として 広く用いられている。従来の制約を越える新し い線路として近年提案された線路である。線路 が細線化できるため、半導体基板を誘電体層と した従来の線路に比べてレイアウト面積を小さ くでき、レイアウト設計の自由度を大きくでき る。但し、微細化によって配線抵抗が増大する という問題がある。

薄膜誘電体層付 MMIC の場合、半導体基板を 誘電体層とした従来の MMIC と異なり、薄膜誘 電体層数とその厚みを比較的自由に設定できる。 形成可能な伝送線路が複数有り、加えて、異な る伝送線路を混在させることもできる。複合伝 送線路構造の一例を図3に示す。本例では、薄 膜マイクロストリップ線路とコプレーナ線路と いう2種類の線路を MMIC 上に混在させている [3]。

図3 薄膜誘電体層付 MMIC に形成した 複合伝送線路構造の一例

## 4. 3. 受動素子

MMICには、インダクタ、キャパシタ、抵抗 といった基本受動素子と、方向性結合器、電力 分配器等の機能受動素子を作り込むことができ る。

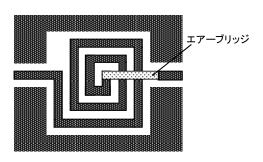

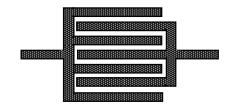

インダクタ素子の構造を図4に示す。MMIC で用いられるインダクタとして、配線を螺旋状 に配置するスパイラルインダクタ、配線を蛇行 させたレイアウトのメアンダライン等を用いる。 また、ミリ波帯等周波数が高い領域では伝送線 路の長さを利用して位相を回転させることもで きる。

(a) スパイラルインダクタ

(b) メアンダライン

図4 インダクタ素子の構造(上面図)ーコプレーナ線路型 MMIC の場合ー

キャパシタ素子の構造を図5に示す。キャパシタとして、窒化シリコン等の薄い誘電体層を介して電極を対向させた MIM (metal-insulator-metal) キャパシタ、あるいは、電極を針状の細長いメタルパターンを複数持つ形とし、ペアとなる電極の針状メタルパターンを交互に近接配置したインターディジタルキャパシタを用いる。

(a) MIM キャパシタ (断面図)

(b) インターディジタルキャパシタ(上面図) 図5 キャパシタ素子の構造

抵抗は、抵抗層として、n+層等のトランジスタに使われる層の一部を流用する場合と、抵抗専用層を用意する場合とがある。所望の抵抗値となるサイズを持つ抵抗層パターンの両端に電極を付けた構造である。特に、大電流を流す場合や、抵抗値が小さい場合には、許容電流量に留意してサイズを決める必要がある。

### 5. MMIC 回路設計例

#### 5. 1. MMIC 增幅器

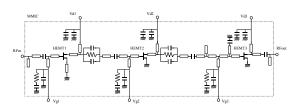

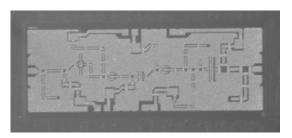

MMIC の一例として、K 帯 3 段 GaAs HEMT MMIC ドライバ増幅器を紹介する。GaAs HEMT MMIC ドライバ増幅器の回路図を図 6 に、チップ写真を図 7 に示す。MMIC には、HEMT が 3 つと整合回路が集積されている。所望の周波数帯域内のリプルを低減する目的で、高域通過フィルタを整合回路部に設けた。増幅器に使用された HEMT は、ゲート長(lg:gate length)が 0.25 μm、1 段目のゲート幅(wg:gate width)が 100 μm、2 段目の wg が 300 μm、3 段目の wg が 800 μm である。MMIC のサイズは、1.6 mm×3.9 mm である。GaAs 基板厚は 70 μm である。MMIC の伝送線路種類はコプレーナ線路である。

図 6 GaAs HEMT MMIC ドライバ増幅器の回路図

図 7 GaAs HEMT MMIC ドライバ増幅器のチップ写真

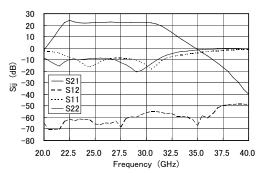

増幅器の小信号特性を図8に示す。増幅器は26.0 GHz で、小信号利得が22.6 dB、VSWRinが1.93、VSWRoutが2.13という特性を得た。 安定化係数 K は 0.5GHz~40GHz 周波数帯域内で1.0 以上であった[4]。

図8 GaAs HEMT MMIC ドライバ増幅器の小信号特性

# 5. 2. レイアウト設計例

5. 1節で紹介したドライバ増幅器に用いた 高域通過フィルタを例として、フィルタ回路特 性のレイアウト依存性を述べる。

まず、高域通過フィルタの高周波特性を、評価サンプルを用いて詳細に評価した。フィルタ は高周波電流が流れる領域に置かれるため、高

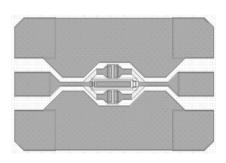

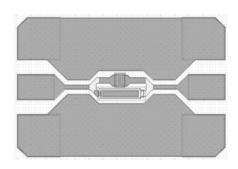

(a) CRC タイプ

(b) RCR タイプ

(c) CR タイプ

図9 高域通過フィルタ評価サンプルのレイアウトと回路トポロジー

周波領域での電流分布に対し適するレイアウトを持つことが必要である。そこで高周波電流分布に対応した、分布定数的、高周波的影響を考

慮したレイアウトを持つフィルタと、考慮しないレイアウトを持つフィルタとで、フィルタの高周波特性にどのような差が生じるかを見積もった。評価サンプルとして異なるレイアウトを持つ3種類のフィルタ、すなわち、CRC タイプ、RCR タイプ、CR タイプのフィルタを準備した。

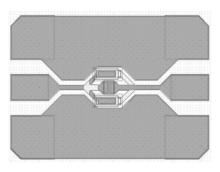

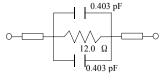

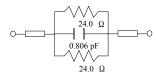

図9に高域通過フィルタ評価サンプルのレイアウトと回路トポロジーを示す。フィルタは、GaAs チップ表面のキャパシタと抵抗で構成され、全ての素子が並列接続されるという単純な構造を持つ。評価サンプル用の引出し線の種類は、コプレーナ線路である。フィルタの、合計の容量値および合計の抵抗値は、3種のフィルタ間で共通にした。

CRC タイプフィルタは、2つのキャパシタと 1つの抵抗から構成され、抵抗が中心に置かれ、 抵抗の両側にキャパシタが置かれるレイアウト を持つ。RCR タイプフィルタは、1つのキャパ シタと2つの抵抗から構成され、キャパシタが 中心に置かれ、キャパシタの両側に抵抗が置か れるレイアウトを持つ。CR タイプフィルタは、 1つのキャパシタと1つの抵抗から構成される。 フィルタのレイアウトサイズは、プロセス許容 範囲内で最小サイズとした。

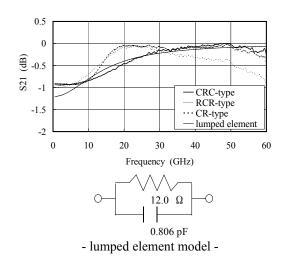

フィルタの通過特性の測定結果を図10に示す。図中に、3種類のフィルタ評価サンプルの 測定値と、比較用の集中定数素子モデルを用い た計算値を表示した。加えて、集中定数素子モ デルの回路図も示した。

3種類のフィルタの特性は、レイアウトに依存して異なる。CRC タイプのフィルタのみが、遮断周波数近傍の準ミリ波帯において、S21 の値が単調増加する特性を示している。また、CRC タイプのフィルタは集中定数素子モデルを用いた計算値に最も近い特性を示している。遮断周波数より高い高周波領域において、S21 の値は3種類のフィルタの内 CRC タイプが最も高く、RCR タイプが最も低いことが判る。60 GHz でのフィルタの通過損の値は、CRC タイプが 0.26

dB、RCR タイプが 0.90 dB、CR タイプが 0.44 dB である。測定結果より、高周波領域で優れた特性を示すフィルタは CRC タイプであることが確認できた。

図10 高域通過フィルタの通過特性 (測定値)

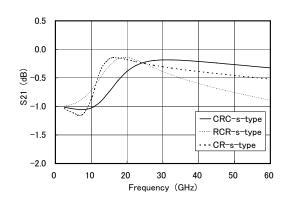

図11 高域通過フィルタの通過特性 (計算値)

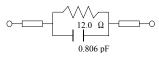

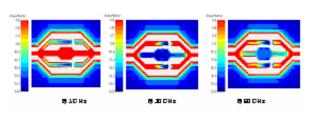

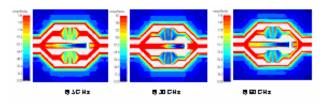

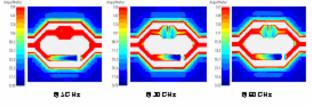

次に、2次元電磁界解析シミュレーションにより、高域通過フィルタの特性を計算した。フィルタの通過特性の計算値を図11に、フィルタの電流分布図を図12に示す。フィルタの測定値と電磁界シミュレーションによる計算値は、高周波領域において同様の特徴を持つことが判る。すなわち、高周波電流が高域通過素子であるキャパシタに流れ、低域通過素子である抵抗に流れないレイアウトを持つフィルタほど、高周波領域で優れた特性を示すことが判る。

以上の例のように、MMIC の特性はレイアウトによって大きく異なる場合があるので、レイアウト設計の際には考慮が必要である。

(a) CRC タイプ

(b) RCR タイプ

(c) CR タイプ

図12 同サイズを持つ高域通過フィルタ 電流分布図(計算値)

#### 6. おわりに

以上、MMICの設計経験が浅い技術者向けに、MMICを設計する際に知っていることが望ましい基本事項を述べた。高周波回路では、動作周波数が高い程、部品や素子の寸法が動作周波数での波長と近づくため、設計が難しくなる。MMIC化は、回路を小形に実現できる、重要な技術である。MMIC固有の設計時に考慮するべき事項は、回路の目的に合うトランジスタとMMICの構造を選ぶこと、適する回路トポロジーとそこに用いる素子の構造を選ぶことである。さらに、集中定数を用いる回路設計を基礎とした上で、分布定数的な考え方、電磁界的な考え方を適所に用い、回路設計とレイアウト設計を

することである。本講義が MMIC を設計する技 術者の助けになれば幸いである。

# 参考文献

- [1] 伊藤康之 他, "MMIC 技術の基礎と応用", 株式会社リアライズ社, 1996 年.

- [2] 相川正義 他, "モノリシックマイクロ波集 積回路 (MMIC)", 社団法人電子情報通信学会, 1997 年.

- [3] Naoko Ono, et al., "60-GHz-band Monolithic HEMT Amplifiers Using BCB Thin Film Layers on GaAs Substrates," IEICE TRANSACTIONS on Electronics, VOL.E82-C, NO.7, pp.1073-1079, July 1999.

- [4] Naoko Ono, et al., "Millimeter-wave Monolithic GaAs HEMT Medium-Power Amplifier Having Low-Loss, CRC High-Pass Equalizer Circuits," IEICE TRANSACTIONS on Electronics, VOL.E87-C, NO.5, pp.733-741, May 2004.